# A Mathematical Approach for Compiling and Optimizing Hardware Implementations of DSP Transforms

Peter A. Milder August 2010

A Dissertation Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical and Computer Engineering Carnegie Mellon University Pittsburgh, Pennsylvania, USA

Copyright © 2010 by Peter A. Milder. All Rights Reserved.

### **Abstract**

Linear signal transforms (such as the discrete Fourier transform) are frequently used in digital signal processing and related fields. Algorithms for computing linear transforms are well-understood and typically have a high degree of regularity and parallelism, making them well-suited for implementation as sequential datapaths on field-programmable gate arrays or application-specific integrated circuits. Nonetheless, transforms are difficult to implement due to the large number of algorithmic options available and ways that algorithms can be mapped to sequential datapaths. Further, the best choices depend heavily on the resource budget and performance goals of the target application. Thus, it is difficult for a designer to determine which set of options will best meet a given set of requirements.

This thesis proposes the Spiral hardware generation framework, a hardware compilation and optimization tool based on a mathematical formula language. A formula written in this language specifies a particular transform algorithm executed using a particular sequential datapath. This language allows high-level representation of sequential hardware structures that reuse datapath elements multiple times in the computation of a transform. The language accomplishes this by providing a formal connection between structure in the algorithm and sequential reuse in the datapath. This proposed language drives a hardware compilation system that takes as input a problem specification with directives that define characteristics of the desired datapath; the system then automatically generates an algorithm, maps the algorithm to a datapath, and outputs synthesizable register transfer level Verilog.

This thesis evaluates the generated designs when synthesized for field-programmable gate array or application-specific integrated circuit. Its evaluations consider designs across multiple transforms, datatypes, and design goals, and its results show that Spiral is able to automatically provide

a wide tradeoff between cost (e.g., area, power) and performance. This tradeoff space compares well with existing benchmarks, but allows the designer much more flexibility to find the design best suited to his or her needs.

## **Acknowledgments**

First, I would like to thank my academic advisor James C. Hoe for his support and guidance of my graduate studies. His advice and encouragement have made this work possible, and I am very grateful for his time, effort, and expertise.

I also owe a great amount of thanks to Markus Püschel and Franz Franchetti. My work would not be possible without their efforts and ideas, and our collaborations were extremely valuable. I sincerely thank them both for their mentorship and for serving on my thesis committee.

I also thank my committee members Larry Pileggi and David Padua for their valuable feedback and comments, which have helped improve my work and this thesis.

Thank you also to the entire Spiral research team. I owe a special debt of gratitude to Yevgen Voronenko for building so much of the infrastructure that my work depends on and for never tiring of helping me understand it. Thank you also to Jeremy Johnson and José Moura, who have always been encouraging and helpful towards me, and whose efforts to establish Spiral were crucial to all of our work. I have been honored to work on the Spiral team with many graduate students, postdocs, and researchers, especially Volodymyr Arbatov, Christian Berger, Srinivas Chellappa, Bob Koutsoyannis, Marek Telgarsky, Wei Yu, and Qian Yu.

I would also like to thank the other researchers with whom I have collaborated, including Yannis Benlachtar, Rachid Bouziane, Eric Chung, Madeleine Glick, and Robert Killey.

I consider myself lucky to spend my time around so many talented, interesting, and entertaining people: my fellow graduate students. Thank you to those listed above as well as Kristen Dorsey, Brian Gold, Adam Hartman, Yoongu Kim, Peter Klemperer, Ruy Ley-Wild, Brett Meyer, Eriko Nurvitadhi, Michael Papamichael, Aliaksei Sandryhaila, Stephen Somogyi, Evangelos Vlachos, Kai Yu, and many more.

I thank the Department of Electrical and Computer Engineering and its staff, especially Reenie Kirby, Matt Koeske, and Elaine Lawrence.

Lastly, I would like to thank my family for their love and support. Thank you to Lauren Heller, my parents Gary and Frances Milder, and my sister Amy Milder.

This work was supported by NSF through awards 0325687 and 0702386, and by DARPA through the DOI grant NBCH1050009 and the ARO grant W911NF0710416.

## **Contents**

| 1 | Intr | oductio | n                                          | 1  |

|---|------|---------|--------------------------------------------|----|

|   | 1.1  | Motiva  | ation                                      | 1  |

|   | 1.2  | Thesis  | Overview                                   | 2  |

|   | 1.3  | Contri  | butions                                    | 3  |

|   | 1.4  | Organi  | ization                                    | 4  |

| 2 | Bac  | kground | d: Linear Transforms and Algorithms        | 5  |

|   | 2.1  | Linear  | Transforms                                 | 5  |

|   |      | 2.1.1   | Discrete Fourier Transform                 | 6  |

|   |      | 2.1.2   | Two-Dimensional Discrete Fourier Transform | 6  |

|   |      | 2.1.3   | Real Discrete Fourier Transform            | 6  |

|   |      | 2.1.4   | Discrete Cosine Transform Type 2           | 7  |

|   | 2.2  | Formu   | la Representation of Transform Algorithms  | 8  |

|   |      | 2.2.1   | Matrix product                             | 9  |

|   |      | 2.2.2   | Tensor product                             | 10 |

|   |      | 2.2.3   | Diagonal matrices                          | 11 |

|   |      | 2.2.4   | Permutations                               | 11 |

|   |      | 2.2.5   | Computational kernels                      | 12 |

|   |      | 2.2.6   | Example                                    | 13 |

|   | 2.3  | Transf  | form Algorithms                            | 13 |

|   |      | 2.3.1   | Discrete Fourier Transform                 | 13 |

|   |      | 2.3.2   | Two-Dimensional Discrete Fourier Transform | 18 |

CONTENTS

|   |      | 2.3.3    | Real DFT                                    | 18 |

|---|------|----------|---------------------------------------------|----|

|   |      | 2.3.4    | Discrete Cosine Transform                   | 22 |

| 3 | Forr | nula-Ba  | sed Datapath Representation                 | 25 |

|   | 3.1  | Stream   | ing Reuse                                   | 25 |

|   |      | 3.1.1    | Streaming reuse of other formula constructs | 26 |

|   | 3.2  | Iterativ | re Reuse                                    | 29 |

|   |      | 3.2.1    | Iterative Reuse of Other Formula Constructs | 30 |

|   | 3.3  | Formu    | la-Based Hardware Model                     | 30 |

|   | 3.4  | Combi    | ning Streaming and Iterative Reuse          | 31 |

|   | 3.5  | Summa    | ary                                         | 34 |

| 4 | Auto | omatic ( | Compilation from Formula to Datapath        | 36 |

|   | 4.1  | Hardw    | are Directives                              | 36 |

|   | 4.2  | Formu    | la Generation: From Transform to Algorithm  | 38 |

|   | 4.3  | Formu    | la Rewriting: Algorithm to Hardware Formula | 39 |

|   |      | 4.3.1    | Rewriting for Streaming Reuse               | 39 |

|   |      | 4.3.2    | Rewriting for Iterative Reuse               | 41 |

|   | 4.4  | RTL G    | eneration: Hardware Formula to RTL Verilog  | 43 |

|   |      | 4.4.1    | Compilation Overview                        | 43 |

|   |      | 4.4.2    | Compilation Stages                          | 45 |

| 5 | Perr | nuting S | Streaming Data                              | 49 |

|   | 5.1  | Proble   | m                                           | 49 |

|   | 5.2  | Existin  | g Approaches                                | 50 |

|   | 5.3  | Genera   | d Streaming Permutations                    | 52 |

|   |      | 5.3.1    | Parameterized Datapath                      | 52 |

|   |      | 5.3.2    | Problem Formulation                         | 55 |

|   |      | 5.3.3    | Algorithm                                   | 58 |

|   | 5 4  | Evalua   | tion                                        | 59 |

VII CONTENTS

| 6 | Trai | nsform Algorithms                                            | 63  |

|---|------|--------------------------------------------------------------|-----|

|   | 6.1  | Discrete Fourier Transform                                   | 63  |

|   | 6.2  | Two-Dimensional Discrete Fourier Transform                   | 68  |

|   | 6.3  | Real Discrete Fourier Transform                              | 70  |

|   | 6.4  | Discrete Cosine Transform                                    | 71  |

| 7 | Eval | uation                                                       | 73  |

|   | 7.1  | Methodology                                                  | 74  |

|   |      | 7.1.1 FPGA                                                   | 75  |

|   |      | 7.1.2 ASIC                                                   | 76  |

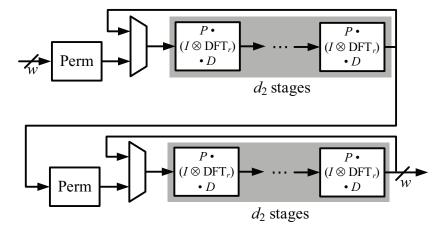

|   | 7.2  | Design Space Exploration Example                             | 77  |

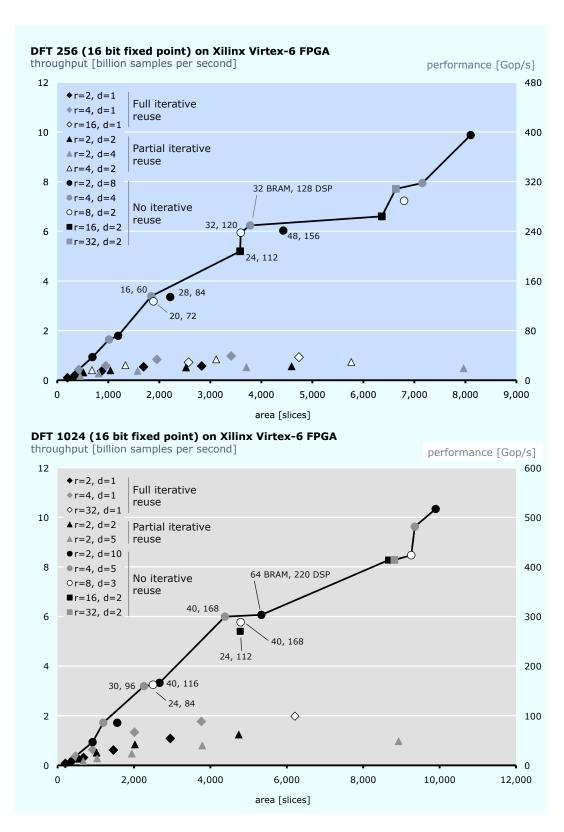

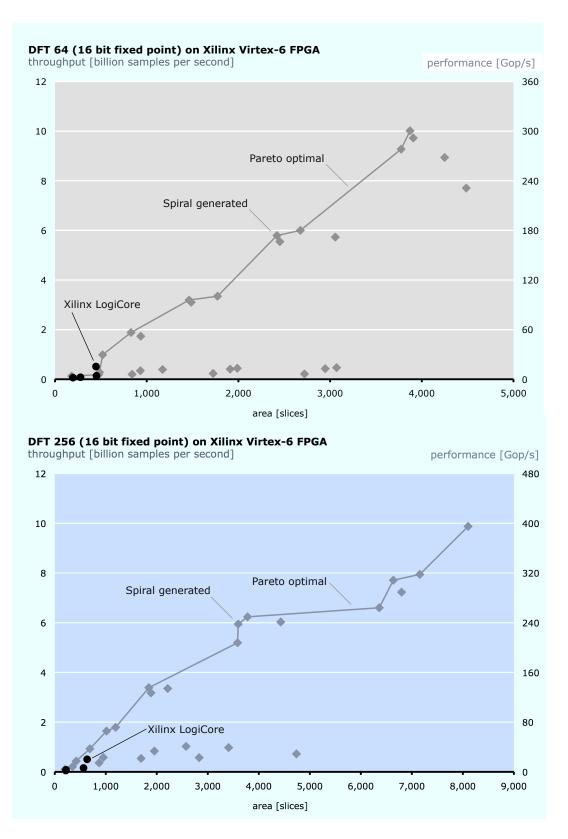

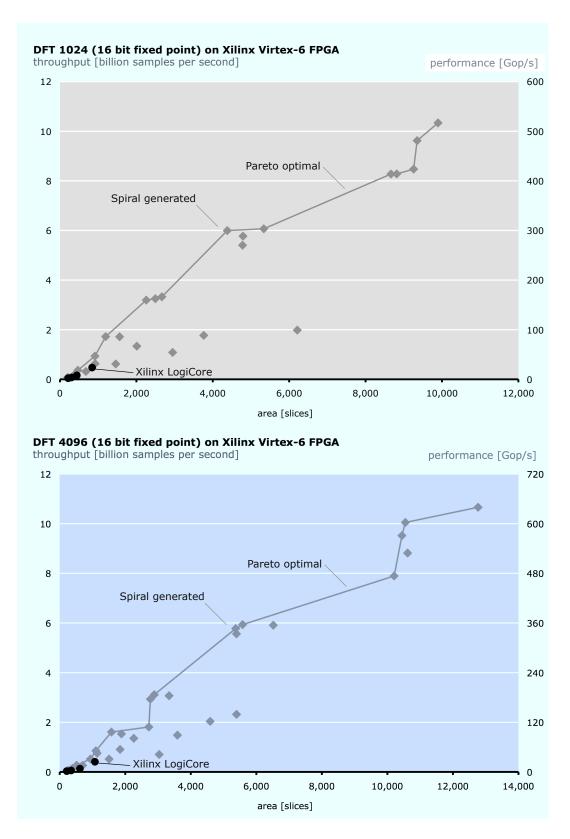

|   | 7.3  | Discrete Fourier Transform on FPGA                           | 80  |

|   |      | 7.3.1 Fixed Point                                            | 80  |

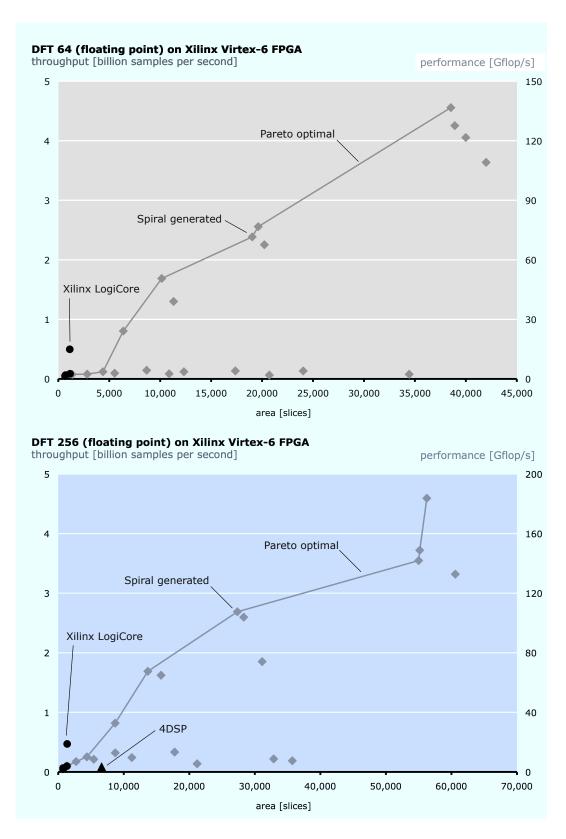

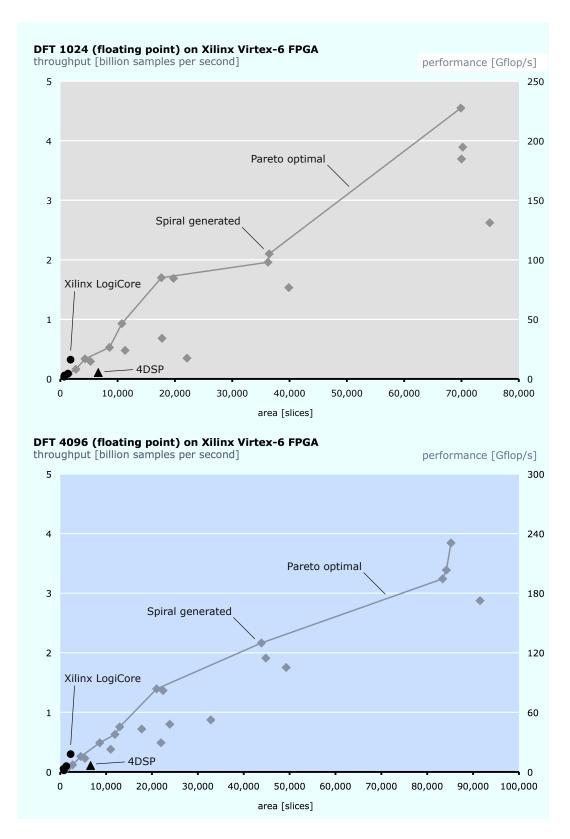

|   |      | 7.3.2 Floating Point                                         | 81  |

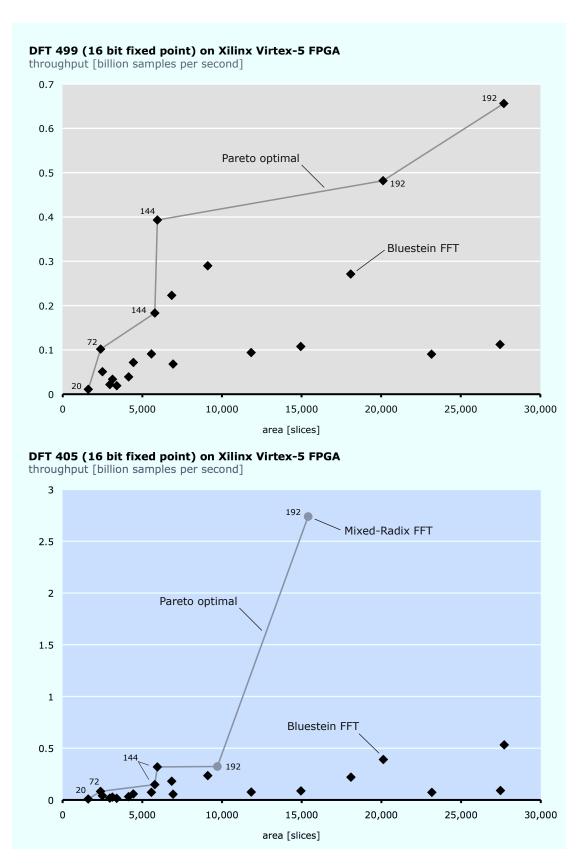

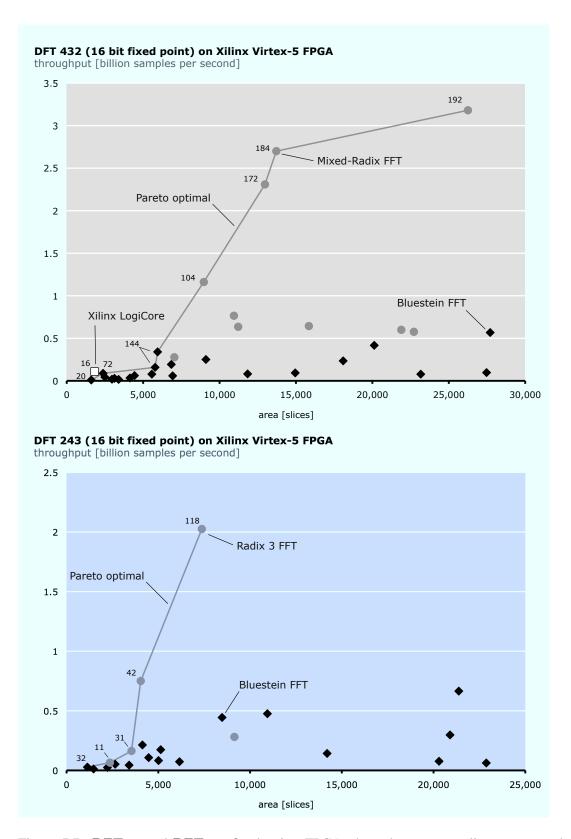

|   |      | 7.3.3 DFT with Non-Power-of-Two Problem Size                 | 87  |

|   | 7.4  | Discrete Fourier Transform on ASIC                           | 90  |

|   |      | 7.4.1 Baseline: Maximum Frequency                            | 90  |

|   |      | 7.4.2 Frequency Scaling                                      | 99  |

|   |      | 7.4.3 Power/Area Optimization Under Throughput Requirement   | 101 |

|   | 7.5  | Other Transforms                                             | 104 |

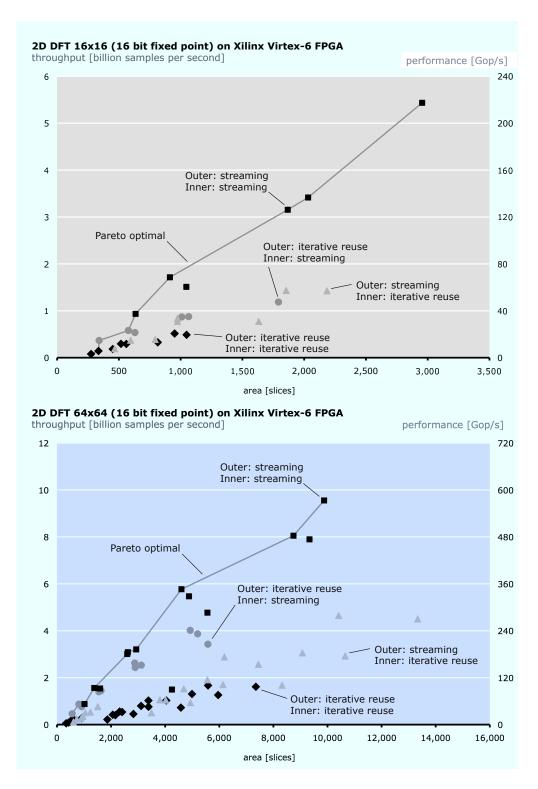

|   |      | 7.5.1 Two-dimensional DFT                                    | 104 |

|   |      | 7.5.2 Real Discrete Fourier Transform                        | 104 |

|   |      | 7.5.3 Discrete Cosine Transform                              | 106 |

|   | 7.6  | Evaluation Summary                                           | 106 |

| 8 | Ortl | nogonal Frequency-Division Multiplexing for Optical Networks | 110 |

|   | 8.1  | FPGA Prototype                                               | 110 |

|   | 8.2  | ASIC Design Study                                            | 114 |

| 9 | Rela | ted Work                                                     | 116 |

|   | 9.1  | Formula-based Hardware Representation                        | 116 |

CONTENTS viii

|    | 9.2  | Hardw    | are Implementation of Transforms | 116 |

|----|------|----------|----------------------------------|-----|

|    |      | 9.2.1    | Fully-Folded DFT Processors      | 117 |

|    |      | 9.2.2    | Pipelined DFT Implementations    | 117 |

|    |      | 9.2.3    | Increasing Flexibility           | 120 |

|    |      | 9.2.4    | Multiplierless Implementations   | 121 |

|    |      | 9.2.5    | Systolic Arrays                  | 122 |

|    |      | 9.2.6    | Non-two-power sizes              | 122 |

|    |      | 9.2.7    | Other Transforms                 | 123 |

|    | 9.3  | High-L   | evel Synthesis                   | 123 |

|    | 9.4  | Stream   | ing Permutations                 | 124 |

| 10 | Conc | clusions | and Future Work                  | 126 |

|    | 10.1 | Overvi   | ew                               | 126 |

|    | 10.2 | Directi  | ons for Future Work              | 128 |

## **List of Tables**

| 3.1 | Formula-based hardware modeling.                                  | 31  |

|-----|-------------------------------------------------------------------|-----|

| 4.1 | Rewriting rules for streaming reuse                               | 40  |

| 4.2 | Rewriting rules for iterative reuse                               | 42  |

| 5.1 | Summary of memories required for streaming permutation structures | 59  |

| 7.1 | Latency (cycles) of arithmetic operators at given frequencies     | 77  |

| 8.1 | RMS error and SNR for IDFT $_{128}$ designs                       | 113 |

| 9.1 | Summary of pipelined DFT architectures                            | 118 |

| 9.2 | Summary of pipelined DFT architectures, normalized                | 120 |

# **List of Figures**

| 2.1 | Formulas and combinational datapaths                                                                   | 9  |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 2.2 | Pease FFT dataflow for $\mathrm{DFT}_{2^3}$                                                            | 15 |

| 2.3 | Iterative FFT dataflow for $\mathrm{DFT}_{2^3}.$                                                       | 17 |

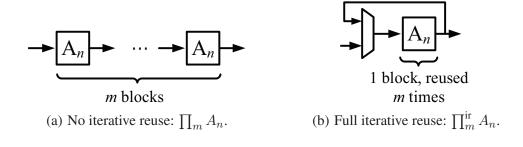

| 3.1 | Examples of streaming reuse                                                                            | 26 |

| 3.2 | Examples of iterative reuse                                                                            | 29 |

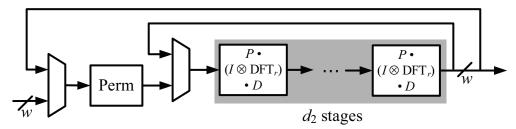

| 3.3 | Combining streaming and iterative reuse                                                                | 32 |

| 4.1 | Block diagram of hardware compilation system                                                           | 37 |

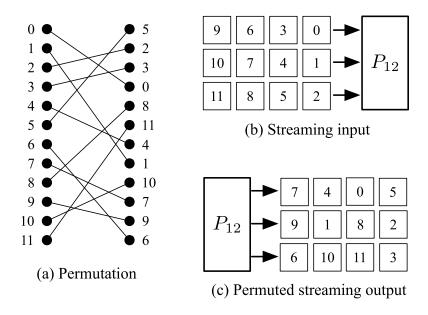

| 5.1 | Examples: permutation and streaming permutation                                                        | 50 |

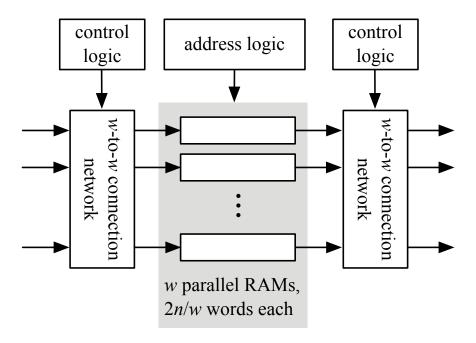

| 5.2 | Streaming permutations, bit matrix method                                                              | 51 |

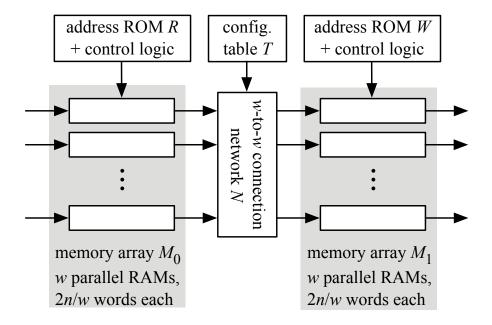

| 5.3 | Streaming permutations, general method                                                                 | 53 |

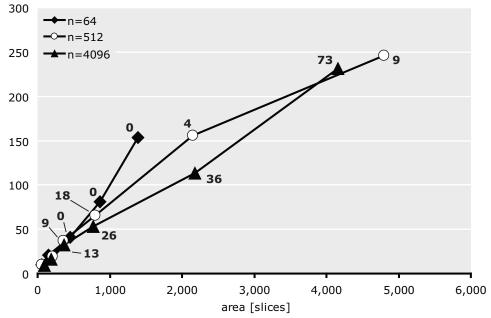

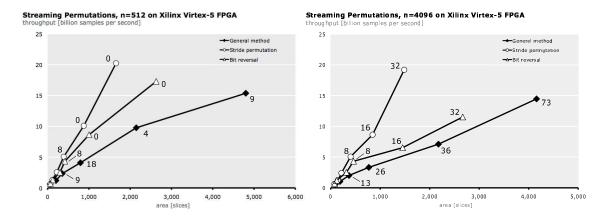

| 5.4 | Throughput versus slices for $n=64,512,4096$ . Labels: number of BRAMs                                 | 60 |

| 5.5 | Comparison of streaming permutation methods                                                            | 62 |

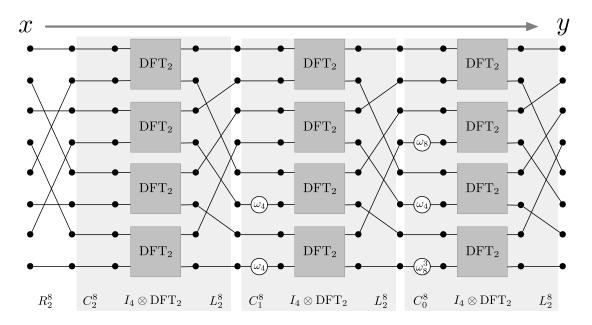

| 6.1 | Pease FFT: $\mathrm{DFT}_{2^3}$ , no sequential reuse                                                  | 65 |

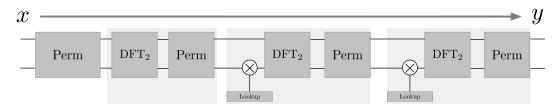

| 6.2 | Pease FFT: DFT $_{2^3}$ , streaming width $w=2,\ldots,\ldots$                                          | 65 |

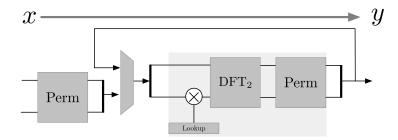

| 6.3 | Pease FFT: DFT $_{2^3}$ , streaming width $w=2$ , depth $d=1,\ldots,\ldots$                            | 66 |

| 6.4 | Illustrations of DFT $_{n\times n}$                                                                    | 69 |

| 7.1 | Exploring $\mathrm{DFT}_{256}$ and $\mathrm{DFT}_{1024}$ , fixed point, FPGA, throughput versus slices | 78 |

| 7.2 | $\mathrm{DFT}_{64}$ and $\mathrm{DFT}_{256},$ fixed point, FPGA, throughput versus slices              | 82 |

| 7.3 | $DFT_{1024}$ and $DFT_{4096}$ , fixed point, FPGA, throughput versus slices                            | 83 |

| 7.4 | $\mathrm{DFT}_{64}$ and $\mathrm{DFT}_{256}$ , floating point, FPGA, throughput versus slices          | 85 |

xi LIST OF FIGURES

| 7.5  | $\mathrm{DFT}_{1024}$ and $\mathrm{DFT}_{4096},$ floating point, FPGA, throughput versus slices        | 86  |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 7.6  | $\mathrm{DFT}_{499}$ and $\mathrm{DFT}_{405}$ , fixed point, FPGA, throughput versus slices            | 88  |

| 7.7  | $\mathrm{DFT}_{432}$ and $\mathrm{DFT}_{243},$ fixed point, FPGA, throughput versus slices             | 89  |

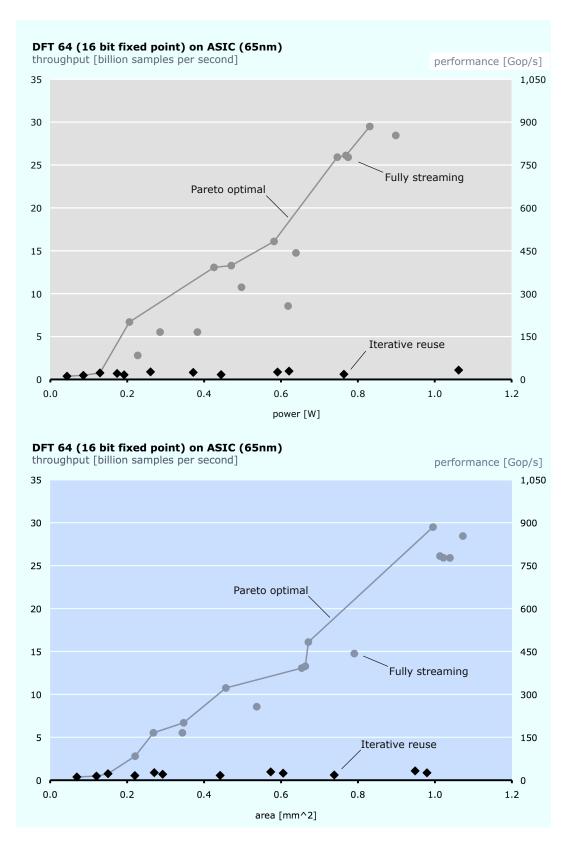

| 7.8  | $\mathrm{DFT}_{64}$ throughput versus power and area, fixed point on 65nm ASIC                         | 91  |

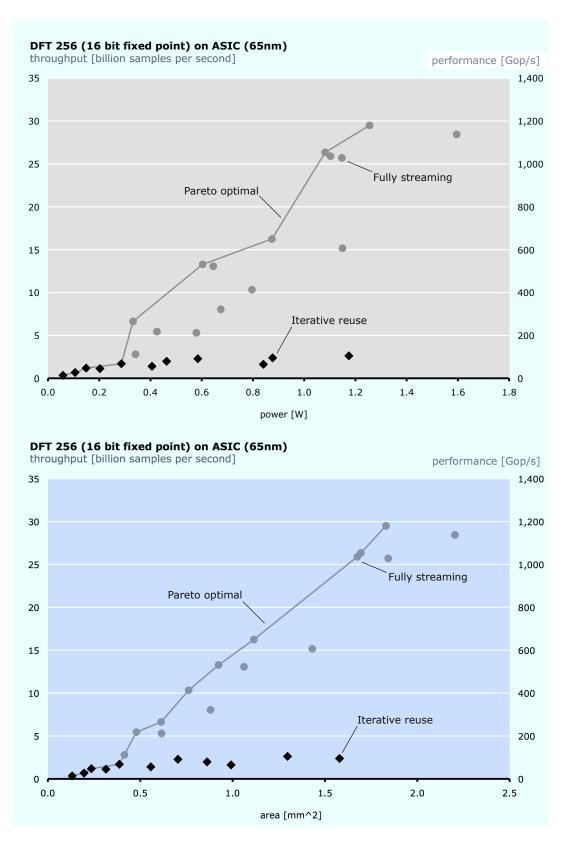

| 7.9  | $\mathrm{DFT}_{256}$ throughput versus power and area, fixed point on 65nm ASIC. $$                    | 92  |

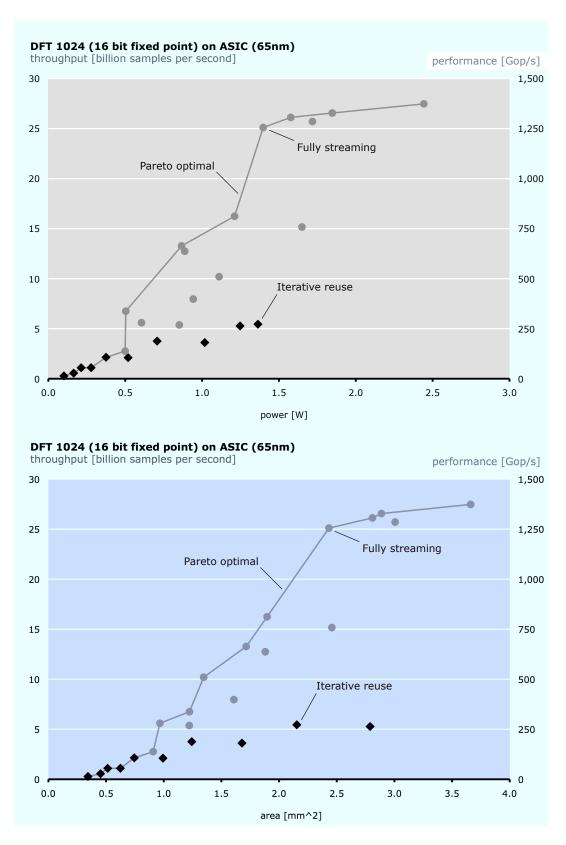

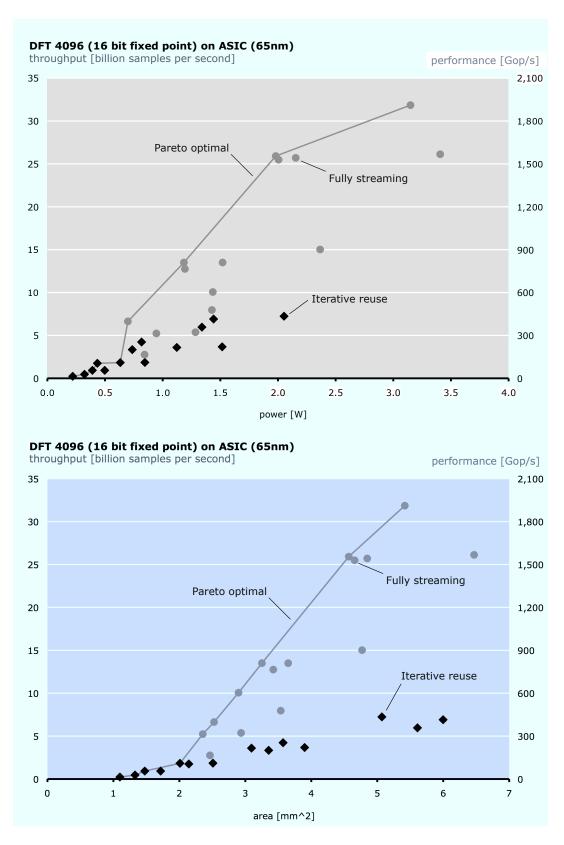

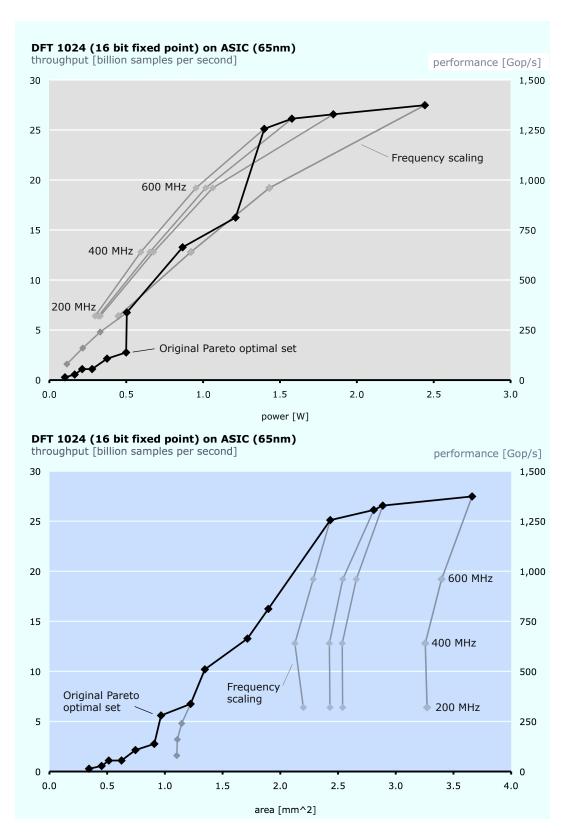

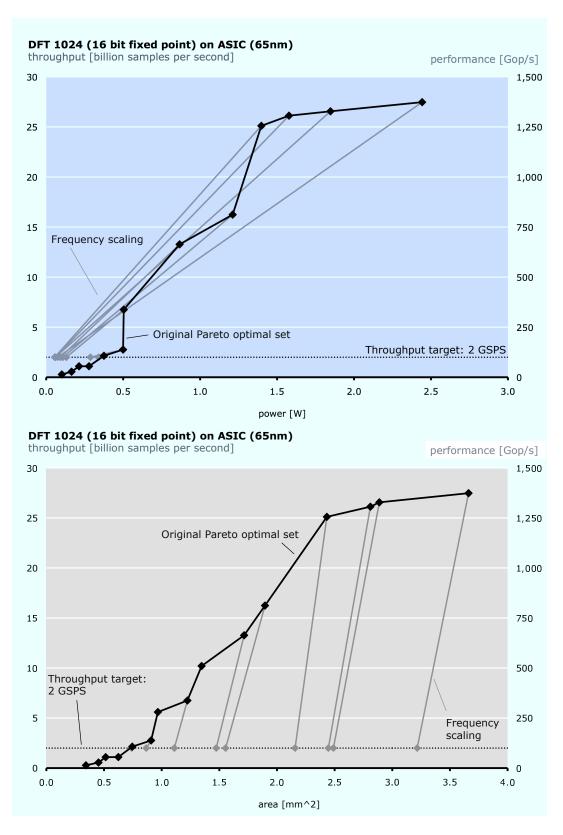

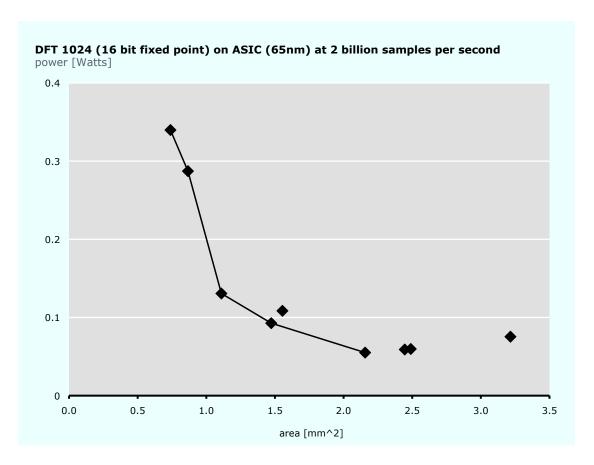

| 7.10 | $\mathrm{DFT}_{1024}$ throughput versus power and area, fixed point on 65nm ASIC                       | 93  |

| 7.11 | $\mathrm{DFT}_{4096}$ throughput versus power and area, fixed point on 65nm ASIC                       | 94  |

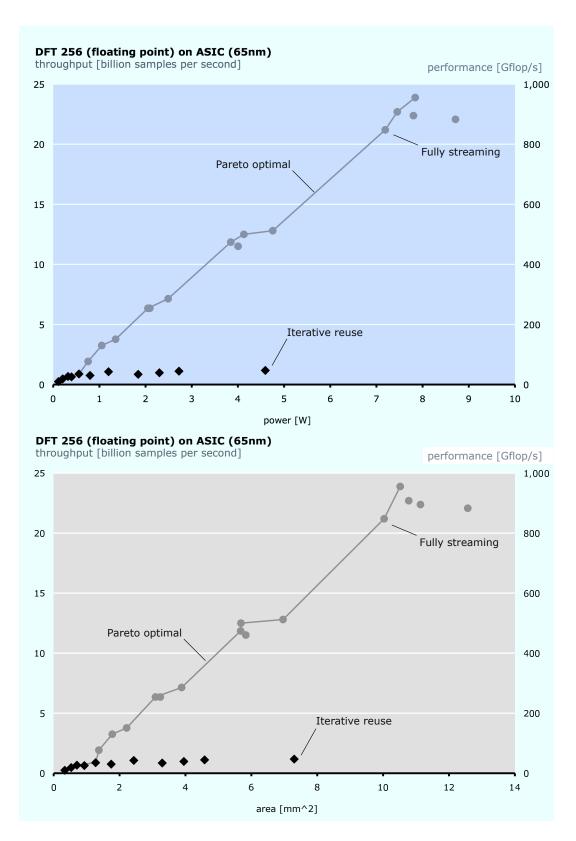

| 7.12 | $\mathrm{DFT}_{64}$ throughput versus power and area, floating point on 65nm ASIC                      | 95  |

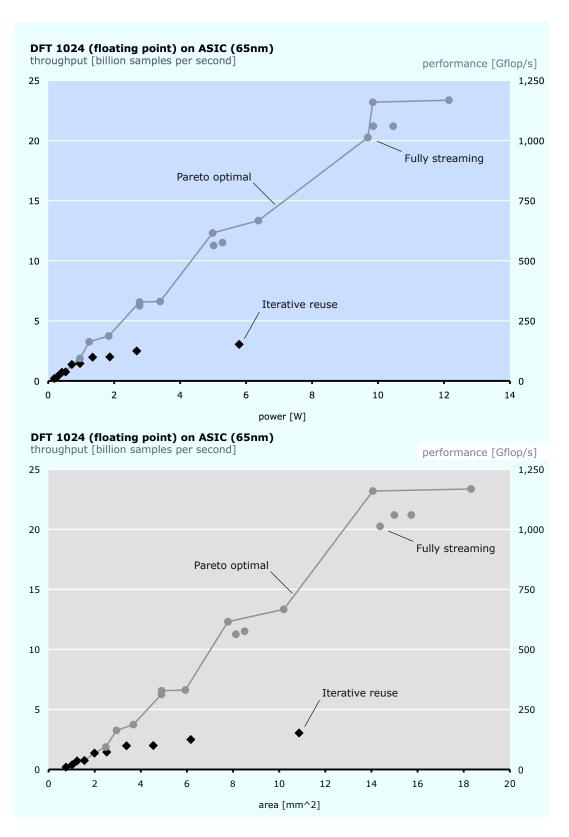

| 7.13 | $\mathrm{DFT}_{256}$ throughput versus power and area, floating point on 65nm ASIC                     | 96  |

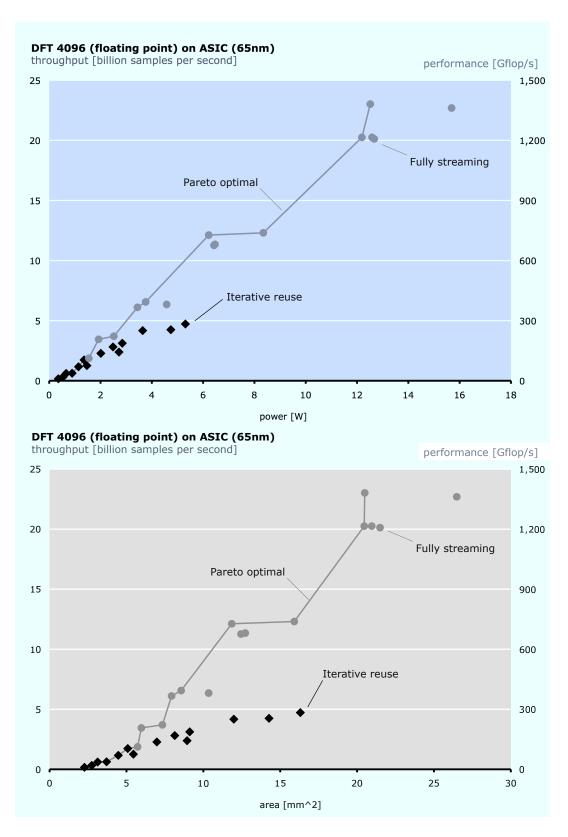

| 7.14 | $\mathrm{DFT}_{1024}$ throughput versus power and area, floating point on 65nm ASIC                    | 97  |

| 7.15 | $\mathrm{DFT}_{4096}$ throughput versus power and area, floating point on 65nm ASIC                    | 98  |

| 7.16 | $DFT_{1024}$ , throughput versus power/area with frequency scaling                                     | 100 |

| 7.17 | $DFT_{1024},$ throughput versus power/area on ASIC, with frequency scaling                             | 102 |

| 7.18 | $\mathrm{DFT}_{1024}$ , fixed point, power versus area, with frequency scaling                         | 103 |

| 7.19 | $\rm DFT$ -2D $_{16\times16}$ and DFT -2D $_{64\times64},$ fixed point, throughput versus area on FPGA | 105 |

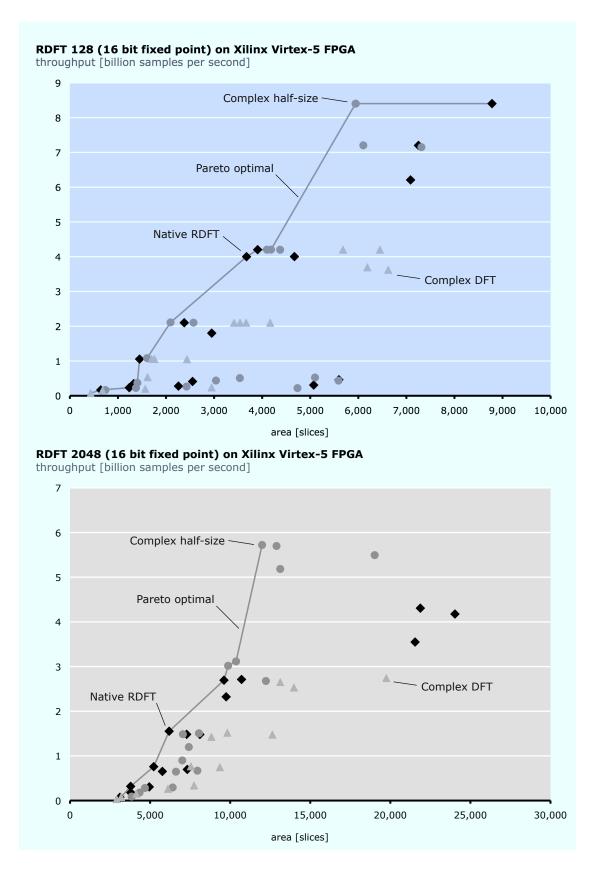

| 7.20 | $RDFT_{128}$ and $RDFT_{2048},$ fixed point, throughput versus area on FPGA                            | 107 |

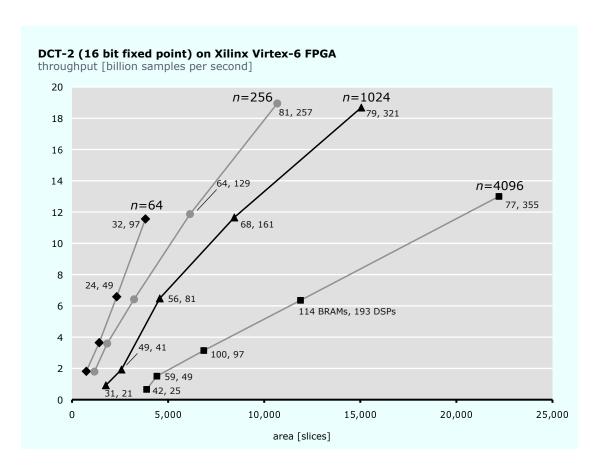

| 7.21 | $\operatorname{DCT-2}_n$ , fixed point, throughput versus area on FPGA                                 | 108 |

|      |                                                                                                        |     |

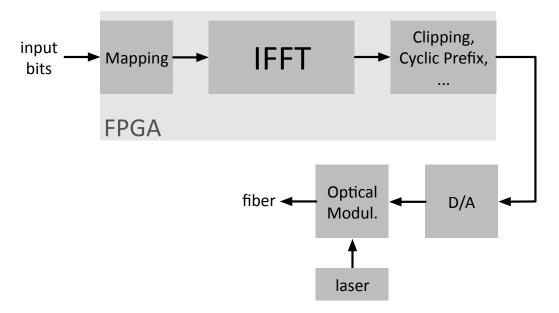

| 8.1  | OFDM FPGA prototype transmitter                                                                        | 111 |

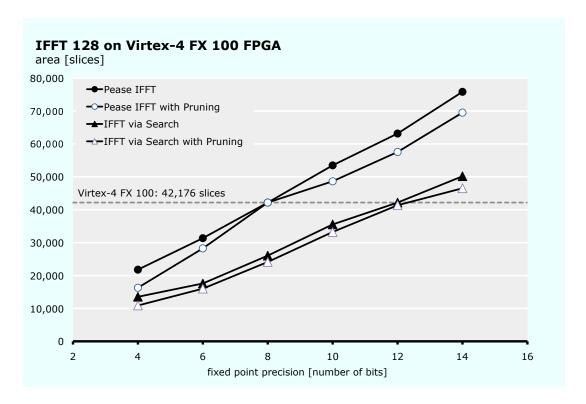

| 8.2  | Area versus fixed-point precision of IDFT cores for OFDM on FPGA                                       | 112 |

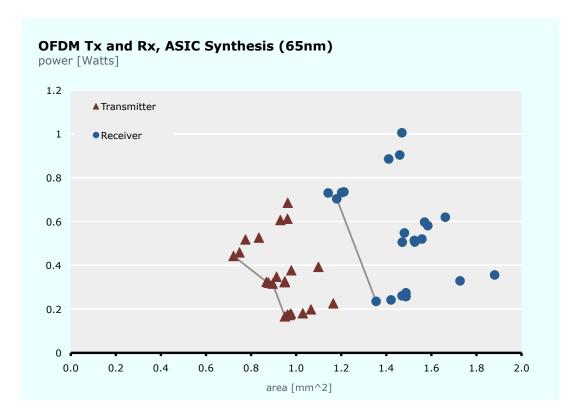

| 8.3  | Power versus area for OFDM transmitters and receivers                                                  | 115 |

### **Chapter 1**

### Introduction

#### 1.1 Motivation

Linear signal transforms such as the discrete Fourier transform or discrete cosine transform are ubiquitous in digital signal processing (DSP), scientific computing, and communication applications. Algorithms for computing linear transforms are highly structured and regular, and they exhibit large amounts of parallelism. For these reasons, algorithms in this domain are well-suited for hardware implementation as a sequential datapath on a field-programmable gate array (FPGA) or application-specific integrated circuit (ASIC). This inherent algorithmic structure leads to a large amount of freedom in the way a given algorithm maps to a datapath. Coupled with the fact that multiple algorithmic options are typically available for a given transform, this means that the combined algorithm/datapath space is far too large for a designer to explore easily.

Further, the algorithmic and datapath options are mutually restricting; the best choice in one domain depends on which choices are made in the other. However, designers typically do not have the tools available to reason about both sets of options at once. Moreover, the best choices for both algorithm and datapath structure are highly dependent on the context: an application's specific performance goals and cost requirements.

Typically, a designer attempting to build a customized hardware implementation of a linear signal transform will alternate between: (a) exploring algorithms to be executed on a specific type of datapath, and (b) exploring different datapaths to execute a specific type of algorithm. Either way, the designer reasons about one portion of the problem while keeping an implicit mapping between

1.2. Thesis Overview 2

algorithm and datapath in his or her mind. This human-driven exploration process is difficult and slow, and few designers have the required experience with both algorithm and hardware design domains needed to arrive at the options best suited for their application requirements. Often, designers resort to using solutions from IP vendors that provide common designs across a few cost/performance tradeoff points.

#### 1.2 Thesis Overview

This thesis addresses these problems by introducing a high-level mathematical framework for automatically generating customized hardware implementations of linear DSP transforms. This system covers a wide range of algorithmic and datapath options and frees the designer from the difficult process of manually performing algorithmic and datapath exploration. The designs produced cover a wide cost/performance tradeoff space and are competitive with good hand-designed implementations. The system's automated nature allows easy exploration of a wide space of options without sacrificing the quality of the resulting design.

The key to the proposed system is a domain-specific formula-based language for specifying transform algorithms and sequential datapaths on which to execute them. This language extends the language in [1] to include datapath concepts such as parallelism and explicit datapath reuse, which the designer specifies at a high level of abstraction. A single formula in this extended language specifies one particular algorithm and one specific sequential datapath on which to execute it.

This mathematical language drives a full compilation system that begins with a problem specification and produces a synthesizable register-transfer level Verilog description. This system begins by taking as input a linear signal transform of a given size as well as high-level hardware directives that describe qualities of the desired datapath. Then, the system utilizes a base of algorithmic knowledge to construct a formula that specifies a transform algorithm. Next, the formula is rewritten (based on user-provided directives) to produce a *hardware formula* that explicitly specifies a datapath with sequential reuse of hardware structures. Lastly, the system maps the hardware formula to a corresponding synthesizable register-transfer level Verilog description.

An important challenge in mapping from formula to sequential datapath lies in the hardware implementation of permutations (fixed reorderings of data, commonly occurring in transform algo-

rithms). Permutations are difficult to perform on streaming data because the system must buffer and reorder data elements distributed over a number of cycles. This thesis includes a flexible parameterized architecture for performing any given streaming permutation as well as a discussion and evaluation of the applicability of previous, less flexible methods.

Additionally, this thesis includes an evaluation of designs produced using the proposed generation framework across several transforms (such as the discrete Fourier transform, discrete cosine transform, and others) and two datatypes (single precision floating point and 16 bit fixed point are evaluated here). Results are obtained by synthesizing for FPGA (Xilinx Virtex-6) and ASIC (targeting a commercial 65nm standard cell library). The FPGA results compare performance with resources required, while the ASIC results compare performance with power and area. Results show that Spiral is able to generate designs across a range of cost/performance tradeoffs.

One application for the designs produced using the proposed system is orthogonal frequency-division multiplexing (OFDM) for optical interconnects. Optical OFDM has recently been studied as a way to reduce the complexity and cost of optical components for short distance links (for example, in data centers) [2] or to improve long-distance transmission performance (telecommunications applications) [3]. Optical OFDM depends heavily on the discrete Fourier transform and imposes a high throughput requirement on it. This thesis includes a study of real-time implementations of optical OFDM, using hardware cores automatically generated by the proposed framework.

#### 1.3 Contributions

To summarize, the contributions of this thesis include:

- a formula-based language for specifying transform algorithms and corresponding sequential datapaths,

- an automatic compilation tool that produces synthesizable register-transfer level Verilog,

- a parameterized, scalable architecture capable of performing any fixed streaming permutation,

- an evaluation of the designs produced using this system, spanning multiple transforms, data types, and platforms, and

1.4. Organization 4

• an application study of real-time implementations of optical OFDM using generated designs.

### 1.4 Organization

This thesis is organized as follows. Chapter 2 describes relevant background material on linear transforms, their algorithms, and algorithmic specification in the aforementioned formula language. Then, Chapter 3 explains the proposed mathematical formula language for describing sequentially reused datapaths. Next, Chapter 4 outlines the automatic compilation process and describes each step from transform to formula to hardware implementation. Chapter 5 discusses one important compilation problem: implementing permutations on streaming data. It presents a proposed flexible solution for any fixed streaming permutation. Chapter 6 examines transform algorithms in this context and illustrates the correspondence between algorithmic and datapath structures. Chapter 7 evaluates the designs produced with this methodology on FPGA and ASIC. Chapter 8 presents an application study where generated cores for the discrete Fourier transform are utilized within real-time systems implementing orthogonal frequency-division multiplexing (OFDM) for optical networks. Lastly, Chapter 9 examines related work and Chapter 10 presents concluding remarks.

### Chapter 2

## **Background: Linear Transforms and**

## **Algorithms**

This chapter presents background material on linear transforms and fast algorithms for their computation. First, Section 2.1 defines linear transforms and gives relevant examples. Then, Section 2.2 shows how a mathematical formula language can specify transform algorithms and how formulas written in it are directly translated to combinational datapaths. This algorithm-specification language explicitly captures regularity or repetition within algorithms. Later, Chapter 3 will show how this regularity leads to hardware structures with explicit datapath reuse. Lastly, Section 2.3 defines the algorithms considered in this thesis.

#### 2.1 Linear Transforms

A linear transform on n points is defined by a dense  $n \times n$  matrix. Applying the transform to an n point input vector is then a matrix-vector multiplication. For example, the discrete Fourier transform on n points is defined as  $y = DFT_n x$ , where x and y are respectively n point input and output vectors, and

$$DFT_n = [\omega_n^{k\ell}]_{0 \le k, \ell \le n}, \quad \omega_n = e^{-2\pi i/n}.$$

In this notation, DFT<sub>n</sub> is an  $n \times n$  matrix, and k and  $\ell$  represent the row and column of a given element (respectively). Thus, computing a four-point DFT (with input vector x and output vector

2.1. Linear Transforms 6

y) is the matrix-vector product:

$$\begin{bmatrix} y_0 \\ y_1 \\ y_2 \\ y_3 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & i & -1 & -i \\ 1 & -1 & 1 & -1 \\ 1 & -i & -1 & i \end{bmatrix} \cdot \begin{bmatrix} x_0 \\ x_1 \\ x_2 \\ x_3 \end{bmatrix}.$$

Direct computation of a linear transform by definition requires  $O(n^2)$  arithmetic operations.

#### 2.1.1 Discrete Fourier Transform

The discrete Fourier transform and its inverse are defined:

$$DFT_n = \left[\omega_n^{k\ell}\right]_{0 \le k, \ell \le n}, \quad \omega_n = e^{-2\pi j/n}$$

(2.1)

$$IDFT_n = (1/n) \cdot \left[\omega_n^{-k\ell}\right]_{0 \le k, \ell \le n}.$$

(2.2)

Also note that

$$DFT_n = (DFT_n)^{\mathsf{T}}.$$

That is, the DFT matrix is symmetric.

#### 2.1.2 Two-Dimensional Discrete Fourier Transform

$$DFT - 2D_{n \times n} = DFT_n \otimes DFT_n, \tag{2.3}$$

where  $\otimes$  is the *tensor* or *Kronecker product*, defined:

$$B \otimes A = [b_k \, _{\ell}A], \quad \text{where } B = [b_k \, _{\ell}].$$

#### 2.1.3 Real Discrete Fourier Transform

When the DFT, which is a complex transform, is performed on real input data (length n), the result is an n point complex output vector with conjugate-even symmetry. Thus, half of its output data is redundant. The real discrete Fourier transform, or RDFT, exploits this property by computing only

the non-redundant outputs, and packing them into a real n point output vector. Depending on the ordering of the output vector, there can be multiple definitions of the RDFT. This thesis uses the following definition for RDFT:

$$RDFT_{n} = \begin{bmatrix} 1 & 1 & 1 & 1 & \dots & 1 \\ 1 & -1 & 1 & -1 & \dots & -1 \\ \cos \frac{2\pi k\ell}{n} \\ \sin \frac{2\pi k\ell}{n} \end{bmatrix}_{0 < k < n/2, \ 0 \le \ell < n}$$

(2.4)

#### 2.1.4 Discrete Cosine Transform Type 2

There are multiple related *types* of discrete cosine transforms (DCTs) and discrete sine transforms (DSTs). This thesis considers the most common, the DCT of type two, defined:

DCT-2 =

$$\left[\cos \frac{k(2\ell+1)\pi}{2n}\right]_{0 < k,\ell < n}$$

. (2.5)

The DCT-2 is easily converted to other related transforms:

$$DCT-3_n = (DCT-2_n)^{-1} = (DCT-2_n)^{\mathsf{T}}$$

$$DST-2_n = \begin{bmatrix} 1 \\ \cdot \cdot \\ 1 \end{bmatrix} \cdot DCT-2_n \cdot \begin{bmatrix} 1 \\ -1 \\ 1 \end{bmatrix}$$

$$DST-3_n = (DST-2_n)^{-1} = (DST-2_n)^{\mathsf{T}}$$

The algorithms that are later presented for DCT-2 can easily be converted to DCT-3, DST-2 and DST-3 in this way.

#### 2.2 Formula Representation of Transform Algorithms

Fast transform algorithms enable the computation of an n point transform using  $O(n \log n)$  arithmetic operations. The term "fast Fourier transform" refers to such an algorithm for computing the discrete Fourier transform. A fast transform algorithm can be expressed as a decomposition of the  $n \times n$  transform matrix into a product of structured sparse matrices. For example,

$$DFT_{4} = \begin{bmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & i \end{bmatrix} \begin{bmatrix} 1 & 1 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & -1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}.$$

(2.6)

Thus, computing  $y = \mathrm{DFT}_4 \cdot x$  is equivalent to multiplying the data vector by each matrix from right to left. A fast algorithm decomposes an  $n \times n$  transform matrix into a product of sparse matrices  $(O(\log n) \text{ many})$ , each which requires O(n) operations. Thus, multiplying the input vector by each of these sparse matrices requires  $O(n \log n)$  operations.

The Kronecker product formalism developed in [1] uses linear algebra concepts to mathematically represent fast transform algorithms by capturing the structure within the sparse matrices of the decomposition. This formalism can serve as the basis for a language that represents transform algorithms as *formulas*, where each term in the formula has a corresponding dataflow interpretation. Thus, a formula in this language can be directly translated into a combinational hardware implementation.

In Backus-Naur form, this language is defined as follows:

$$\begin{array}{ll} \mathbf{matrix}_n ::= \mathbf{matrix}_n \cdots \mathbf{matrix}_n \\ & \mid \prod_{\ell} \mathbf{matrix}_n \\ & \mid I_k \otimes \mathbf{matrix}_m \qquad \text{where } n = km \\ & \mid I_k \otimes_{\ell} \mathbf{matrix}_m \qquad \text{where } n = km \\ & \mid \mathbf{base}_n \end{array}$$

$$\mathbf{base}_n ::= D_n = \mathrm{diag}(d_0, \dots, d_{n-1}) \mid P_n \mid A_n$$

This language is a subset of the signal processing language (SPL) used in Spiral, a program generator for software implementations of linear transforms [4, 5].

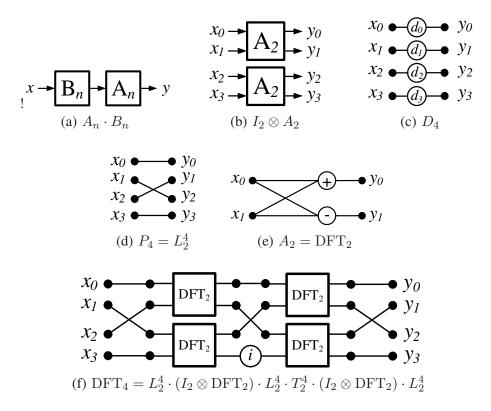

Figure 2.1: Examples of formula elements and their corresponding combinational datapaths.

Next, the following subsections explain each portion of the language, and illustrate the combinational hardware interpretation of each term (in Figure 2.1).

#### 2.2.1 Matrix product

A matrix formula can be decomposed into a product (line 1) or iterative product (line 2) of matrix formulas. Figure 2.1(a) illustrates: if  $y = (A_n B_n) \cdot x$ , then input vector x first is transformed by  $B_n$ , then by  $A_n$  to produce output vector y. Note that the matrices are applied to the data vector from right to left.

The iterative product  $\prod$  is important because it allows the explicit specification of repeated stages that are identical or related. Chapter 3.2 discusses how this repetition is exploited to represent explicit datapath reuse in the proposed hardware compilation and optimization framework.

#### 2.2.2 Tensor product

Line 3 shows that a matrix formula can include the *tensor* (or Kronecker) product of matrices. The  $\otimes$  operator is the *tensor product operator*, defined:

$$B \otimes A = [b_{k,\ell}A], \text{ where } B = [b_{k,\ell}].$$

$I_k$  is the  $k \times k$  identity matrix, so

$$I_k \otimes A_m = egin{bmatrix} A_m & & & & & \\ & A_m & & & & \\ & & \ddots & & & \\ & & & A_m \end{bmatrix},$$

a  $km \times km$  matrix that is *block-diagonal*. When  $I_k \otimes A_m$  is interpreted as dataflow, the  $A_m$  matrix is applied k times in parallel to consecutive regions of the km-length input vector. Figure 2.1(b) illustrates this for k=2, m=2.

Line 4 illustrates an indexed version of the tensor product:

$$I_k \otimes_\ell A_\ell^m = \begin{bmatrix} A_0^m & & & & \\ & A_1^m & & & \\ & & \ddots & & \\ & & & A_{k-1}^m \end{bmatrix},$$

where the index variable  $\ell$  parameterizes the A matrix.

Although this language only supports the tensor product where the left term is the identity matrix, simple identities rewrite some other structures into this form. For example:

$$A_m \otimes I_k = L_m^{km} (I_k \otimes A_m) L_k^{km}, \tag{2.7}$$

where L is the stride permutation matrix defined in (2.8), below. Further,

$$B_k \otimes A_m = (B_k \otimes I_m)(I_k \otimes A_m)$$

$$= L_k^{km}(I_m \otimes B_k)L_m^{km}(I_k \otimes A_m).$$

The regularity expressed by  $I_k \otimes A_m$  is critical to the hardware generation and optimization method proposed in this work. Section 3.1 shows how the regularity represented by this formula is exploited to represent explicit datapath reuse.

#### 2.2.3 Diagonal matrices

This language contains three classes of *base matrices*. First are *diagonal matrices*, written  $D_n$ . A diagonal matrix is one that contains non-zero elements only along its main diagonal:

$$D_n = \operatorname{diag}(d_0, d_1, \dots, d_{n-1}) = \begin{bmatrix} d_0 & & & \\ & d_1 & & \\ & & \ddots & \\ & & & d_{n-1} \end{bmatrix},$$

where the  $d_{\ell}$  are constants. Multiplying a vector by  $D_n$  results in scaling each element by one constant. Figure 2.1(c) illustrates this for  $D_4$ . This thesis uses  $D_n$  to represent any generic diagonal matrix of size n. A diagonal matrix can be defined with a parameter, for example  $D_{\ell}^n$ , where  $\ell$  can be the index variable of an indexed tensor product or iterative product.

#### 2.2.4 Permutations

The second class of base matrix is comprised of *permutations*, or fixed reorderings of data elements.  $P_n$  denotes a permutation on n points. As combinational logic, this is implemented as a re-ordering of data by shuffling wires. Figure 2.1(d) illustrates this for a particular permutation on four points. This thesis uses  $P_n$  to represent an arbitrary n point permutation; other letters will be used to define other permutations in transform algorithms. A permutation can be viewed as a matrix or as a mapping on the indices of data elements. For example,  $L_m^n$  represents the stride-by-m permutation

on n points, which permutes data according to

$$L_m^n: i \cdot (n/m) + j \mapsto j \cdot m + i, \quad 0 \le i < m, \ 0 \le j < n/m,$$

(2.8)

where in + j represents the given output index, and jm + i is the corresponding input index. For example,

Another important permutation is the base-r digit reversal permutation on n points:  $R_r^n$ .

$$R_r^{r^t} = \prod_{\ell=0}^{t-1} (I_{r^{t-\ell-1}} \otimes L_r^{r^{\ell+1}}).$$

(2.9)

When r=2, this permutation is called the *bit reversal* permutation.

#### 2.2.5 Computational kernels

The final class of base matrices is comprised of *computational kernels* Matrix  $A_n$  denotes a generic  $n \times n$  computational kernel that takes in n data elements and produces n output elements. Typically, such a kernel is only used when n is small; a combinational datapath is formed by directly implementing a matrix-vector multiplication. One example of such a kernel is

$$DFT_2 = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix},$$

which is illustrated in Figure 2.1(e). Computational kernels can also be parameterized by index variables:  $A_{\ell}^{n}$ .

#### **2.2.6** Example

A linear transform algorithm specified in this language can be directly mapped to a combinational datapath. For example, the Cooley-Tukey FFT (fast Fourier transform) [6] can be written as

$$DFT_{mn} = L_m^{mn} \cdot (I_n \otimes DFT_m) \cdot L_n^{mn} \cdot T_n^{mn} \cdot (I_m \otimes DFT_n) \cdot L_m^{mn}, \qquad (2.10)$$

where  $L_m^{mn}$  is the stride permutation (2.8),  $T_n^{mn}$  is a diagonal matrix of "twiddle factors" (as specified in [7]):

$$T_n^{mn} = \bigoplus_{k=0}^{m-1} \left( \bigoplus_{\ell=0}^{n-1} \omega_{mn}^{k\ell} \right), \quad \omega_n = e^{-2\pi i/n}, \tag{2.11}$$

and  $\bigoplus$  is the direct sum operator. So,

$$T_2^4 = \bigoplus_{k=0}^1 \left( \bigoplus_{\ell=0}^1 \omega_4^{k\ell} \right) = \bigoplus_{k=0}^1 \left( \omega_4^{k\cdot 0} \oplus \omega_4^{k\cdot 1} \right) = \omega_4^{0\cdot 0} \oplus \omega_4^{0\cdot 1} \oplus \omega_4^{1\cdot 0} \oplus \omega_4^{1\cdot 1}$$

$$= \operatorname{diag}(1, 1, 1, i).$$

Figure 2.1(f) shows the corresponding combinational datapath for this algorithm when n=2 and m=2. Again, note that the matrices are applied from left to right.

### 2.3 Transform Algorithms

This section uses the mathematical language defined in Section 2.2 to specify the transform algorithms considered in this thesis. Later, Chapter 6 will explain how these algorithms fit within the proposed hardware/algorithm specification language, and Chapter 7 will evaluate implementations of the algorithms.

#### 2.3.1 Discrete Fourier Transform

$O(n \log n)$  algorithms for the DFT are often called fast Fourier transforms, or FFTs. Note that the DFT is symmetric, so alternate versions of these algorithms may be obtained by transposing the final formula, using property  $(AB)^T = B^T A^T$ . Additionally, these algorithms can be converted into algorithms for the IDFT by taking the complex conjugate and scaling as defined in (2.2).

Cooley-Tukey FFT. The Cooley-Tukey FFT (fast Fourier transform) algorithm [6] recursively decomposes a DFT of size mn into DFTs of size m and n. It is given by

$$DFT_{mn} = L_m^{mn} \cdot (I_n \otimes DFT_m) \cdot L_n^{mn} \cdot T_n^{mn} \cdot (I_m \otimes DFT_n) \cdot L_m^{mn}, \qquad (2.12)$$

where L and T are as defined previously.

**Pease FFT.** The Pease FFT [8] is an iterative algorithm for the DFT that can be derived from the Cooley-Tukey FFT (as shown in [9]). It is given by

$$DFT_{r^t} = \left(\prod_{\ell=0}^{t-1} L_r^{r^t} \cdot (I_{r^{t-1}} \otimes DFT_r) \cdot C_\ell^{r^t}\right) \cdot R_r^{r^t}, \tag{2.13}$$

where C is a diagonal matrix of twiddle factors:

$$C_{\ell}^{r^t} = L_{r^t-\ell-1}^{r^t} \cdot (I_{r^{\ell}} \otimes T_{r^t-\ell-1}^{r^t-\ell}) \cdot L_{r^{\ell+1}}^{r^t},$$

where L, R and T are as defined previously.

Here, the DFT of size  $r^t$  is computed by first reordering data, then passing through t stages, each which scales data, performs parallel DFT<sub>r</sub> computations, and then reorders the data with  $L_r^{r^t}$ .

Parameter r is called the radix. Higher radices give fewer stages, but each stage is more complicated. As the radix increases, the arithmetic cost of the algorithm decreases, because fewer non-trivial multiplications are performed (although the improvement diminishes as r increases).

A key characteristic of the Pease FFT is that the data vector is accessed in the same order in each of the t iterations. In the formula, this can be seen in the fact that only the diagonal matrix C depends on iteration index  $\ell$ . Thus, the only change from stage to stage is in the constants the data vector is scaled by.

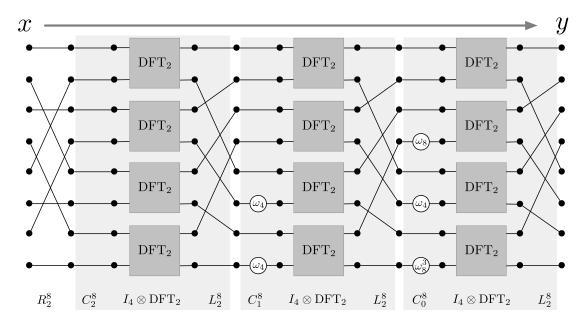

Figure 2.2 illustrates the dataflow for the Pease algorithm for DFT $_{2^3}$ :

$$\left(\prod_{\ell=0}^2 L_2^8 \cdot (I_4 \otimes \mathrm{DFT}_2) \cdot C_\ell^8\right) \cdot R_2^8.$$

The formula is read from right to left, but the dataflow is drawn from left to right. So, Figure 2.2 takes in input vector x on the left, passes it through permutation  $R_2^8$ , then through three stages

Figure 2.2: Pease FFT dataflow for DFT $_{2^3}$ .

(indicated with shaded background). Each stages performs a scaling by a diagonal matrix C, four parallel DFT<sub>2</sub> computations, and permutation  $L_2^8$ . Note that multiplications by 1 are omitted from the diagram, and that  $C_0^8 = I_8$ .

**Iterative Cooley-Tukey FFT.** Similar to the Pease FFT, the Iterative Cooley-Tukey algorithm can also be derived from (2.12), but it results in a different structure.

$$DFT_{r^t} = \left(\prod_{\ell=0}^{t-1} (I_{r^\ell} \otimes DFT_r \otimes I_{r^{t-\ell-1}}) \cdot (I_{r^\ell} \otimes T_{r^{t-\ell-1}}^{r^{t-\ell}})\right) \cdot R_r^{r^t}, \tag{2.14}$$

where all matrices are as previously defined. By utilizing the property given in (2.7) and restructuring terms, this algorithm can be expressed

$$DFT_{r^t} = L_r^{r^t} \left( \prod_{\ell=0}^{t-1} \left( I_{r^{t-1}} \otimes DFT_r \right) \left( I_{r^\ell} \otimes \left( E_\ell^{r^{t-\ell}} \cdot Q_\ell^{r^{t-\ell}} \right) \right) \right) R_r^{r^t}, \tag{2.15}$$

where E is a diagonal matrix of twiddle factors:

$$E_{\ell}^{r^{t-\ell}} = L_{r^{t-\ell-1}}^{r^{t-\ell}} \cdot T_{r^{t-\ell-1}}^{r^{t-\ell}} \cdot L_r^{r^{t-\ell}},$$

and Q is a product of two stride permutations:

$$Q_{\ell}^{r^{t-\ell}} = L_{r^{t-\ell-1}}^{r^{t-\ell}} \cdot (I_r \otimes L_r^{r^{t-\ell-1}}).$$

This thesis will utilize the restructured algorithm (2.15), and refer to it as the Iterative FFT. This algorithm is similar to the Pease FFT: both compute  $\mathrm{DFT}_{r^t}$  using t stages, each stage consisting of a permutation, a scaling by constants, and parallel  $\mathrm{DFT}_r$  computations. However, there is one important difference: in each iteration, the Pease algorithm performs a permutation on  $r^t$  points and multiplies the vector by an  $r^t$  point diagonal matrix. In contrast, the permutation and diagonal matrix in this algorithm grow *smaller* as the stages progress. This means in stage  $\ell$ , the algorithm performs  $r^\ell$  parallel permutations on  $r^{t-\ell}$  points. Chapter 6 will show how these differences lead to a different type of hardware implementations than are obtained from the Pease algorithm.

Figure 2.3 illustrates the dataflow for the Iterative FFT algorithm for DFT $_{23}$ :

$$\mathrm{DFT}_{2^3} = L_2^8 \left( \prod_{\ell=0}^2 \left( I_4 \otimes \mathrm{DFT}_2 \right) \left( I_{2^\ell} \otimes \left( E_\ell^{2^{3-\ell}} \cdot Q_\ell^{2^{3-\ell}} \right) \right) \right) R_2^8.$$

Again, the formula is applied from right to left, while the diagram takes its input x on the left side and produces its output y on the right. First, the data vector is permuted by  $R_2^8$ . Then, it goes through three stages, separated with shaded boxes. Note that the first stage consists only of one column of  $I_4 \otimes \mathrm{DFT}_2$ , because  $E_2^2$  and  $Q_2^2$  are both equal to  $I_2$  and thus do not require hardware.

**Mixed-radix FFT.** The mixed-radix algorithm (based on (2.12)) breaks down a DFT of size  $r^k s^\ell$  into multiple DFTs of sizes  $r^k$  and  $s^\ell$ :

$$DFT_{r^k s^{\ell}} = L_{r^k}^{r^k s^{\ell}} \cdot (I_{s^{\ell}} \otimes DFT_{r^k}) \cdot L_{s^{\ell}}^{r^k s^{\ell}} \cdot T_{s^{\ell}}^{r^k s^{\ell}} \cdot (I_{r^k} \otimes DFT_{s^{\ell}}) \cdot L_{r^k}^{r^k s^{\ell}}.$$

(2.16)

Then, the DFT<sub> $r^k$ </sub> and DFT<sub> $s^\ell$ </sub> matrices are decomposed using radix r and s algorithms such as (2.13) or (2.15).

**Bluestein.** The Bluestein FFT [10] is a convolution-based algorithm for any problem size n. It is typically used when the problem size makes it difficult or impossible to perform with the other algorithms. The Bluestein algorithm performs the DFT by scaling the input vector and convolving it with pre-computed coefficients. The convolution of two n length signals can be performed as

Figure 2.3: Iterative FFT dataflow for  $DFT_{2^3}$ .

point-wise multiplication of length m>2n-1 in the frequency domain. This allows a DFT of any given size to be computed using DFTs of two-power size, at the expense of additional operations. This algorithm is given by:

$$DFT_n = D_{n \times m}^{(2)} \cdot IDFT_m \cdot D_m^{(1)} \cdot DFT_m \cdot D_{m \times n}^{(0)},$$

(2.17)

where  $m=2^{\lceil\log_2(n)\rceil+1}$  is the smallest power of two greater than 2n-1, and the D matrices are diagonal matrices that scale the vector by constant values.  $D_{m\times n}^{(0)}$  and  $D_{n\times m}^{(2)}$  are rectangular matrices, so in addition to scaling the data,  $D_{m\times n}^{(0)}$  extends the input data vector from n points to m points (by zero padding), and  $D_{n\times m}^{(2)}$  shortens the output data vector from m points to n points (by discarding unneeded data).

#### 2.3.2 Two-Dimensional Discrete Fourier Transform

Using the definition of the two-dimensional DFT and a property of the tensor product, the *row-column* algorithm can be derived:

DFT -2D<sub>n×n</sub> =

$$(I_n \otimes DFT_n) \cdot L_n^{n^2} \cdot (I_n \otimes DFT_n) \cdot L_n^{n^2}$$

=  $\prod_{\ell=0}^{1} \left( (I_n \otimes DFT_n) \cdot L_n^{n^2} \right)$  (2.18)

Then, one-dimensional DFT algorithms such as (2.13), (2.15), or (2.16) can be used to compute the DFT<sub>n</sub>.

Other algorithms for computing multi-dimensional DFT not considered in this thesis include the vector-radix algorithm [11] and the Dimensionless FFT algorithm [12].

#### 2.3.3 Real DFT

Complex half-size Real DFT. An RDFT of size n can be computed using a complex DFT of size n/2 and a post-processing step, as shown in [13]:

$$RDFT_n = ((K_2''' \otimes I_2) \cdot (I_{n/4} \otimes_{\ell} A_4(\ell)) \cdot ((K_2''')^{-1} \otimes I_2)) \cdot \overline{DFT_{n/2}},$$

(2.19)

where

$$A_4(0) = \begin{bmatrix} 1 & 1 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix},$$

$$A_4(\ell \neq 0) = \operatorname{diag}(1, 1, 1, -1) \cdot (F_2 \otimes I_2) \cdot \begin{bmatrix} 1/2 & & \\ 1/2 & & \\ & c & -s \\ & s & c \end{bmatrix} \cdot L_2^4 \cdot \begin{bmatrix} 1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 0 & 1 & 0 & -1 \\ -1 & 0 & 1 & 0 \end{bmatrix},$$

$$c = \cos(2\pi \cdot \ell/n)/2, \qquad s = \sin(2\pi \cdot \ell/n)/2,$$

$$F_2 = \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix},$$

$J_n$  is the  $n \times n$  identity matrix with columns reversed, and  $\overline{\mathrm{DFT}_{n/2}}$  converts an  $n/2 \times n/2$  complex matrix into a  $n \times n$  real matrix by replacing each complex element a+bi with

$K_m^{\prime km} = (I_{k+1} \oplus J_{k-1} \oplus I_{k+1} \oplus J_{k-1} \dots) L_m^{km},$

$$\begin{bmatrix} a & -b \\ b & a \end{bmatrix}.$$

This algorithm works by packing the n real data as n/2 complex data, performing a complex DFT $_{n/2}$  using the DFT algorithms presented above in Chapter 2.3.1. Then it permutes data by  $(K^{-1} \otimes I_2)$ , performs one column of computational blocks (A), and finally permutes the data again to output data.

One way to reduce the cost of this implementation is to merge the rightmost permutation stage  $(K^{-1} \otimes I_2)$  with the output permutation on the DFT algorithm. For example, the iterative Cooley-Tukey algorithm (2.15) contains a stride permutation L on its output side, which can be merged directly. Or, the Pease algorithm (2.13) can be transposed, moving the R permutation to the output side (noting that  $R_r^n = (R_r^n)^T$ ).

Although this algorithm has higher arithmetic cost over the native RDFT algorithms presented next, it is useful because all optimizations for the DFT can be immediately applied.

Native RDFT Algorithm: Cooley-Tukey-type. Based on the framework in [13], three algorithms for the RDFT can be defined, similar in structure to the Cooley-Tukey, Pease, and Iterative Cooley-Tukey FFTs (as shown in (2.12), (2.13), and (2.15), respectively). All three algorithms use a helper transform rDFT(u), where

$$RDFT_n = (F_2 \oplus I_{n-2}) \cdot rDFT_n(0).$$

First, a recursive algorithm is defined that will be used as the basis for two iterative algorithms.

$$rDFT_{2km}(u) = \langle K_m^{2km} \mid K_m'^{2km} \rangle_u \left( \bigoplus_{j=0}^{k-1} rDFT_{2m}(r_k(u,j)) \right) (rDFT_{2k}(u) \otimes I_m)$$

(2.20)

$$r_k(u,j) = \begin{cases} j/2k, & u = 0, \\ (u + \lfloor j/2 \rfloor)/k, & u \neq 0 \text{ and } j \text{ even,} \\ (1 - u + \lfloor j/2 \rfloor)/k, & u \neq 0 \text{ and } j \text{ odd} \end{cases}$$

$$K_m^{2km} = ((I_k \oplus J_k \oplus I_k \oplus J_k \dots) L_m^{km}) \otimes I_2,$$

$$K_m'^{2km} = ((I_k \oplus Z_k \oplus I_k \oplus Z_k \dots) L_m^{km}) \otimes I_2,$$

$$Z_k = (I_1 \oplus J_{k-1}),$$

$$\langle A \mid B \rangle_i = \begin{cases} A, & i \neq 0 \\ B, & i = 0 \end{cases},$$

$$B, & i = 0$$

where J is I with the column order reversed. The base cases are given by:

$$\operatorname{rDFT}_{4}(0) = (F_{2} \otimes I_{2}),$$

$$\operatorname{rDFT}_{4}(u \neq 0) = \begin{bmatrix} 1 & & & \\ & 1 & & \\ & & 1 & \\ & & & -1 \end{bmatrix} \cdot \operatorname{rDFT}_{4}(0) \cdot \begin{bmatrix} 1 & & & \\ & 1 & & \\ & & c & -s \\ & & s & c \end{bmatrix} \cdot L_{2}^{4},$$

$$c = \cos(\pi u), \quad s = \sin(\pi u).$$

Native RDFT Algorithm: Constant Geometry. By left-expanding and applying identities to algorithm (2.20), the following constant geometry RDFT algorithm can be derived. Let the problem size be 2km, where  $m=k^p$ ,  $p \ge 1$ . Let  $q=\log_k m$ . The algorithm's radix is 2k.

$$\text{rDFT}_{2km}(0) = V_{k,m}^{2km} \left( \prod_{i=0}^{\log_k m} \left( I_m \otimes_{\ell} \text{rDFT}_{2k}(s_{k,q}(0,0,f_{k,m}(i,\ell))) L_{2m}^{2km} \right) L_{km}^{2km}, \quad (2.21)$$

where

$$f_{k,m}(i,\ell) = \ell \mod m/k^{i},$$

$$s_{k,q}(d,u,f) = \begin{cases} u, & d = q \\ r_{k}(s_{k,q}(d+1,u,f), \lfloor (f \mod k^{d+1})/k^{d} \rfloor), & d \neq q \end{cases}$$

$$V_{k,m}^{2km} = \left(\prod_{\ell=0}^{\log_{k} m-1} \left(K_{m/k^{\ell}}^{\prime m/k^{(\ell-1)}} \oplus \left(I_{k^{\ell}-1} \otimes K_{m/k^{\ell}}^{m/k^{(\ell-1)}}\right)\right)\right) \otimes I_{2}$$

The algorithm begins with a stride permutation, followed by  $\log_k m + 1$  stages, each with a permutation and a radix 2k computational basic block. This block  $(rDFT_{2k}(...))$  is computed using the base case above when k=2, and using (2.20) otherwise. The structure of this algorithm is called constant geometry because the permutation  $L_{2m}^{2km}$  is the same in each stage.

Native RDFT Algorithm: Iterative. Also derived from (2.20) is the following iterative algorithm. Let the problem size be 2km, where  $m = k^p$ ,  $p \ge 1$ . Let  $q = \log_k m$ . Again, the algorithm's

radix is 2k.

$$rDFT_{2km}(0) = V_{k,m}^{2km} \cdot \left( \prod_{i=0}^{q} \left( I_{m/k^i} \otimes W_i^{2 \cdot k^{i+1}} \right) \right)$$

$$\cdot \left( I_m \otimes_{\ell} rDFT_{2k} (s_{k,q-i}(0,0,\lfloor \ell/k^i \rfloor)) \right) \cdot L_m^{2km},$$

(2.22)

where W is a product of stride permutations:

$$W_{i\neq 0}^{2 \cdot k^{i+1}} = \left( I_k \otimes L_{k^{i-1}}^{2 \cdot k^i} \right) \cdot L_{2k}^{2 \cdot k^{i+1}},$$

$$W_0^{2 \cdot k^{i+1}} = I_{2k},$$

and V and s() are as defined above.

This algorithm is similar to the constant geometry RDFT algorithm (2.21). However, unlike (2.21), this algorithm's permutation W grows more local as the algorithm is performed (that is, as i decreases). So, its different stages have different geometry, but the interconnections do not need to span the entire data vector in all stages. The relationship between this algorithm and the constant geometry RDFT algorithm is similar to the relationship between the Iterative and Pease FFT algorithms (2.15) and (2.13).

#### 2.3.4 Discrete Cosine Transform

An algorithm for the DCT of type 2 that is well-suited for hardware implementation is given in [14].

$$DCT-2_{2^k} = \sqrt{\frac{2}{2^k}} \cdot U_{2^k} \cdot \left( \prod_{s=k-1}^0 S_{2^k}^{(s)} (I_{2^{k-s-1}} \otimes L_{2^s}^{2^{s+1}}) \right) P_{2^k}^H.$$

(2.23)

Matrices U and  $P^H$  represent permutations, and S represents one stage of computation, consisting of a 4 point basic block and a diagonal matrix. The full specification of this algorithm is given below.

The structure of this algorithm is similar to the FFT algorithm given in (2.15). It computes a transform of size n in  $\log_2(n)$  stages, each of which reorders data and performs a small computational kernel. The added complexity comes from the M and H matrices, which perform an extra subtraction and data reordering in some basic blocks.

Using the properties of the DCT and DST given in Chapter 2.1.4, this algorithm can easily be used to produce implementations of DCT-3, DST-2, and DST-3. Other similar algorithms can be found in [15] and [16].

Unlike the other algorithms examined in this thesis, this DCT algorithm is defined only for a fixed radix size (two).

Full specification of algorithm (2.23). Matrix S represents one stage of computation, parameterized by stage s:

$$S_{2^k}^{(s)} = (I_{2^{k-1}} \otimes_{\ell} M_2^{(s,\ell)}) \cdot \operatorname{diag}(g_k(\ell,s)) \cdot (I_{2^k-2} \otimes_{\ell} H_4^{(s,\ell)}) \cdot (I_{2^{k-1}} \otimes F_2),$$

where

$$\begin{split} M_2^{(s,\ell)} &= \begin{bmatrix} 1 & 0 \\ -\mu_s(\ell) & 1 \end{bmatrix}, \quad \mu_s(\ell) = \begin{cases} 0, & \ell \mod 2^s = 0, \\ 1, & \ell \mod 2^s \neq 0 \end{cases} \\ g_k(\ell,s) &= (2^{\mu_s(\lfloor \ell/2 \rfloor)} d(2^{k-s-1} + \lfloor \ell/2^{s+1} \rfloor))^{f_k(\ell,s)} \\ d(\ell) &= \cos((h_K(\ell-K) + 1/2)\pi/2K), \quad K = 2^{\lfloor \log_2 \ell \rfloor} \\ h_1(0) &= 0, \quad h_{2N}(2\ell) = h_N(\ell), \quad h_{2N}(2\ell+1) = 2N-1 - h_N(\ell) \\ f_k(\ell,s) &= (\ell \mod 2) + (1 - \tau_0(\ell))(1 - \tau_{k-1}(s)) \\ \tau_\ell(s) &= \begin{cases} 0, & s = \ell \\ 1, & s \neq \ell \end{cases} \\ 1, & s \neq \ell \end{cases} \\ H_4^{(s,\ell)} &= \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 \end{bmatrix} \\ F_2 &= \begin{bmatrix} 1 & 1 \\ 1 & -1 \end{bmatrix} \end{split}$$

Permutations U and  $P^H$  are:

$$\begin{split} U_{2^k} &= \prod_{\ell=0}^{k-2} (I_{2^{k-\ell}} \oplus (I_{2^{k-2}-2^{k-\ell}} \otimes (I_2 \oplus J_2))) \cdot (I_{2^\ell} \otimes L_{2^{k-\ell-1}}^{2^{k-\ell}}), \\ P_{2^k}^H &= [n = h_{2^k}(m)]_{m,n=0,1,\dots,2^k-1}, \end{split}$$

where  $h_{2^k}(m)$  is as defined above, and J is the identity matrix with columns reversed.

# **Chapter 3**

# Formula-Based Datapath

# Representation

The language described in the previous section can represent a wide range of algorithms, but it does not represent *sequential reuse* of datapath components, where one computational block is used multiple times while computing a single problem. Sequential reuse is necessary since the combinational datapaths realized in Chapter 2 are often too large for practical implementation for all but the smallest transform sizes. This chapter describes extensions to this formula language to represent two types of sequential reuse that are relevant for hardware designs. The result is a *hardware language* that allows explicit datapath description at the formula level. Later, this thesis shows that this extended language drives the proposed compilation system, and that it allows description and generation of a wide tradeoff space.

The work described in this section was presented in part in [17].

# 3.1 Streaming Reuse

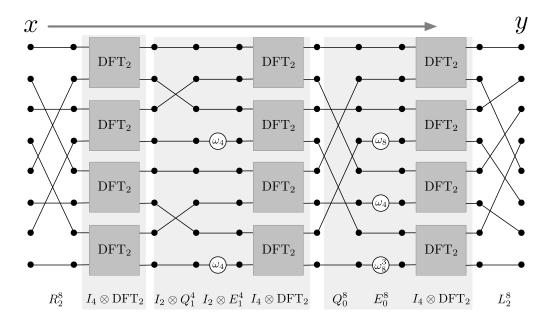

Streaming reuse restructures a datapath with parallel computation blocks into a smaller datapath where data *stream* through the system over multiple cycles.

As shown in Section 2.2, the tensor product  $I_m \otimes A_n$  results in m data-parallel instantiations of the block  $A_n$  (Figure 3.1(a)). However, other structures can also perform the same computation. For example, the tensor product can be interpreted as *reuse in time* (rather than parallelism in

(c) Partial streaming reuse:  $I_{mn/w} \otimes^{sr} (I_{w/n} \otimes A_n)$ .

Figure 3.1: Examples of streaming reuse.

space). Then, one can build a single instance of block  $A_n$  and reuse it over m consecutive cycles (Figure 3.1(b)). Rather than all mn input points entering the system concurrently, they now stream in and out at a rate of n words per cycle. This is defined as *streaming reuse* and represented as  $I_m \otimes^{\operatorname{sr}} A_n$ . The *streaming width* indicates the number of inputs (or outputs) that enter (or exit) a section of datapath during each cycle. Here, the streaming width is n.

The two interpretations of  $\otimes$  can be nested in order to build a partially parallel datapath that is reused over multiple cycles (Figure 3.1(c)). In general,  $I_m \otimes A_n$  can be written as  $I_{mn/w} \otimes^{sr} (I_{w/n} \otimes A_n)$ , which results in a datapath with a streaming width of w, consisting of w/n parallel instances of  $A_n$ , reused over mn/w cycles (w is a multiple of n;  $w \leq mn$ ). Increasing the streaming width increases the datapath's cost and throughput proportionally.

#### 3.1.1 Streaming reuse of other formula constructs

**Indexed tensor product.** Streaming reuse can also be applied to the indexed tensor product

$$I_m \otimes_{\ell} A_{\ell}^n$$

,

where A is an  $n \times n$  matrix parameterized by  $\ell$ . When this construct is streamed with width w=n, one computational block is built that is capable of performing all  $A_{\ell}^n$ ,  $0 \le \ell < m$ . In the worst case, this can lead to a roughly  $m \times$  overhead in the hardware cost, if the m instances cannot share logic between them. However, often this hardware block can be simplified. For example, the DCT-2 algorithm (2.23) presented in Chapter 2.3.4 contains the term

$$(I_{2^{k-1}}\otimes_{\ell}M_2^{(s,\ell)}),$$

where

$$M_2^{(s,\ell)} = \begin{bmatrix} 1 & 0 \\ -\mu_s(\ell) & 1 \end{bmatrix}, \quad \mu_s(\ell) = \begin{cases} 0, & \ell \mod 2^s = 0, \\ 1, & \ell \mod 2^s \neq 0 \end{cases}.$$

When streaming reuse is applied to this formula, only two possible instances of M need to be considered: one that is equivalent to  $I_2$ , and one that performs one subtraction. In hardware, this can be realized as one subtractor and one multiplexer, with a comparator controlling the multiplexing logic.

**Diagonal matrices.** Diagonal matrices scale each data element by a constant. An n point diagonal can easily be streamed with width w by building w multipliers, each holding its own lookup table of n/w constants.

The simplest way to write this as a streaming reuse formula is to reformulate the expression into one that uses  $I \otimes_{\ell}$ . So, a diagonal  $D_n$  with streaming width w is

StreamDiag

$$(D_n, w) = (I_{n/w} \otimes_{\ell}^{sr} ((I_w \otimes_k (D_n \circ f(k))) \circ g(\ell))),$$

(3.1)

where

$$f(k) = \iota_{n/w} \otimes (k)_w,$$

$$g(\ell) = L_{n/w}^n \circ ((\ell)_{n/w} \otimes \iota_w),$$

and  $\iota$ ,  $(\ell)_n$ , and  $\circ$  are indexing functions as defined in [18]:

$$i_n : \mathbb{I}_n \to \mathbb{I}_n; i \mapsto i,$$

$$(j)_n : \mathbb{I}_1 \to \mathbb{I}_n; i \mapsto j,$$

$$g \circ f : \mathbb{I}_m \to \mathbb{I}_N; i \mapsto g(f(i)),$$

$$\mathbb{I}_n = \{0, \dots, n-1\}.$$

First, the diagonal matrix is split into w partial lookup tables. Each holds the values that will be multiplied by inputs from one of the w input ports. The rightmost term in the formula serves to separate the n point diagonal into n/w segments of size w (each corresponding to one cycle of streaming reuse). The values of these segments can then be computed and the results stored in lookup tables.

This representation also allows easy simplification in the case of certain repeated patterns within the diagonal matrix. For example, every other element of twiddle diagonal  $T_2^n$  is equal to 1. So, when this diagonal is streamed (with 2 power streaming width), half of the corresponding multipliers will always multiply by 1. Using this representation makes this situation (and similar ones) easy to recognize within the compiler, allowing automatic removal of the unneeded multiplier.

**Permutation matrices.** Implementing streaming reuse on permutation structures is a difficult problem, but one that is crucially important. A permutation streaming with width w must take in an n point input vector at a rate of w words per cycle. It must buffer the data stream, perform a reordering over the entire n data points, and then stream the data vector out. Chapter 5 presents two methods for constructing this type of system. This thesis uses a streaming permutation wrapper

$$StreamPerm(P_n, w)$$

as a way of representing this structure.

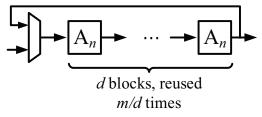

(c) Partial iterative reuse:  $\prod_{m/d}^{ir} (\prod_d A_n)$ .

Figure 3.2: Examples of iterative reuse.

### 3.2 Iterative Reuse

The product of m identical blocks  $A_n$  can be written as  $\prod_m A_n$ . A straightforward interpretation of this is a series of m blocks cascaded (Figure 3.2(a)).

The same computation can be performed by reusing the  $A_n$  block m times (Figure 3.2(b)). Now, the datapath must have a feedback mechanism to allow the data to cycle through the proper number of times. This is called *iterative reuse* and is represented by adding the letters "ir" to the product term:  $\prod_{m}^{ir} A_n$ . By nesting both kinds of product terms, the formula specifies a number of cascaded blocks to be reused a number of times (Figure 3.2(c)). In general,  $\prod_{m} A_n$  can be restructured into  $\prod_{m/d}^{ir} (\prod_{d} A_n)$ , resulting in d cascaded instances of  $A_n$ , iterated over m/d times (where m/d is an integer). The term depth is used to indicate the number of stages built (here, d).

When an iterative reuse datapath is built, it is important that the reused portion of the datapath buffer the entire vector, so the "head" of the data vector does not feed back too soon and collide with its own "tail." This is equivalent to requiring that the latency (in cycles) be at least 1/(its throughput in transforms per cycle). If the datapath does not naturally have this property, it is necessary to add buffers to increase its latency.

#### **3.2.1** Iterative Reuse of Other Formula Constructs

**Dependence on iteration variable.** Iterative reuse can also be applied to the iterative product

$$\prod_{\ell=0}^{m-1}A_\ell^n,$$

where the  $n \times n$  matrix A is parameterized by iteration variable  $\ell$ . If this formula is iteratively reused with depth d=1, then one computational structure capable of performing all of the variants of  $A_n^{(\ell)}$  (where  $0 \le \ell < m$ ) is constructed. In the worst case, m different independent blocks must be built, but often, the structure of the algorithm allows these blocks to be simplified by sharing logic or arithmetic units (for example, the basic block in algorithm (2.21)). This situation is analogous to streaming reuse of the indexed tensor product in Section 3.1.1.

**Diagonal matrices.** Diagonal matrices are often used in product terms with a dependence on the iteration variable:

$$\prod_{\ell=0}^{m-1} D_{\ell}^{n}.$$

This formula can be iteratively reused by storing all mn constants, and adding simple logic to choose from the correct n depending on the value of  $\ell$ . This also works in the streaming case, where it can be written as  $\operatorname{StreamDiag}(D_{\ell}^n, w)$ .

An example of this type of formula construct can be found in the Pease FFT (2.13).

**Permutation matrices.** Similar to diagonal matrices, iterative reuse can also be applied to permutations. If streaming reuse is not used, then this simply is an instance of the generic dependence on iteration variable discussed above. When both streaming and iterative reuse are used, the formula becomes

$$\prod_{\ell=0}^{m-1} \operatorname{StreamDiag}(P_{\ell}^n, w).$$

Chapter 5 describes how this permutation is implemented.

#### 3.3 Formula-Based Hardware Model

Table 3.1 describes rules for deriving the latency, throughput, and an approximate area cost of four basic formula constructs. Given a matrix formula F, the table provides formulas for latency L(F)

| Formula F                                            | Latency $L(F)$                           | Throughput $T(F)$                                  | Area cost $C(F)$          |

|------------------------------------------------------|------------------------------------------|----------------------------------------------------|---------------------------|

| $F_n = A_n^{(0)} \cdot A_n^{(1)} \cdots A_n^{(m-1)}$ | $\sum_{i} (L(A_n^{(i)}))$                | $\min(T(A_n^{(i)}))$                               | $\sum_{i} (C(A_n^{(i)}))$ |

| $F_n = \prod_k^{\mathrm{ir}} A_n$                    | $\max(\frac{k}{T(A_n)}, k \cdot L(A_n))$ | $\min(\frac{T(A_n)}{k}, \frac{1}{k \cdot L(A_n)})$ | $C(A_n) + C(\max)$        |

| $F_{mn} = I_m \otimes A_n$                           | $L(A_n)$                                 | $T(A_n)$                                           | $m \cdot C(A_n)$          |

| $F_{mn} = I_m \otimes^{\mathrm{sr}} A_n$             | $L(A_n)$                                 | $T(A_n)/m$                                         | $C(A_n)$                  |

Table 3.1: Given a matrix formula F, formulas for latency L(F) (cycles), throughput T(F) (transforms per cycle) and approximate area cost C(F) (relative to the area cost of sub-modules).

(cycles), throughput T(F) (transforms per cycle) and approximate area cost C(F) relative to the latency, throughput, and area of F's submodules. The entries of this table can be recursively used to reason about complex formulas. Section 3.4 will give an example for a common formula type that can combine streaming reuse and iterative reuse.

## 3.4 Combining Streaming and Iterative Reuse

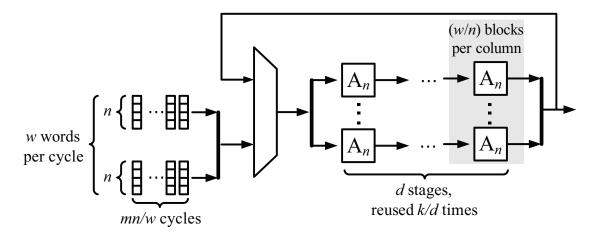

Often, transform algorithms contain the form  $\prod_k (I_m \otimes A_n)$ . This structure can utilize both iterative reuse (due to the  $\prod$ ) and streaming reuse (due to  $I_m \otimes A_n$ ), allowing a wide range of hybrid implementations that exhibit flexibility across two dimensions. One can restructure this formula to have streaming and iterative reuse of parameterized amounts:

$$\prod_{\ell_0=0}^{k/d-1} \inf \left( \prod_{\ell_1=0}^{d-1} (I_{nm/w} \otimes^{\operatorname{sr}} (I_{w/n} \otimes A_n)) \right),$$

where d is the depth of the cascaded stages (ranging from 1 to k; k/d must be an integer). Parameter w is the streaming width, a multiple of n.

This parameterized datapath is illustrated in Figure 3.3. Each stage consists of w/n parallel instances of  $A_n$ ; d stages are built in series. Let  $B_{mn}$  represent this array of dw/n many  $A_n$  blocks. Data are loaded into the cascaded stages at a rate of w per cycle over mn/w cycles. The vector feeds back and passes through the series of stages a total of k/d times.

Latency and throughput. Given this combined reuse example, one can use the structure of the formula to analyze the effect of parameters d and w on the datapath. The following are calculations that correspond to evaluating the general rules from Table 3.1 for the specific parameters of this

Figure 3.3: Combining iterative and streaming reuse:  $\prod_{k/d}^{\text{ir}} \left( \prod_d (I_{nm/w} \otimes^{\text{sr}} (I_{w/n} \otimes A_n)) \right)$ .

combined reuse example (Figure 3.3). These calculations assume that  $B_{mn}$  (the collective block of  $A_n$  blocks) is fully pipelined, i.e., its throughput is dictated by the problem size and streaming width only:  $T(B_{mn}) = w/mn$ . The analysis of latency and throughput for this combined reuse example includes the following two cases:

- Case 1: Iterative reuse. This case occurs when d < k, meaning the data will iterate over the internal block at least 2 times. As discussed in Section 3.2, the internal block's minimum latency is determined by its throughput. So, if  $d \cdot L(A_n) < mn/w$ , buffers are added until they are equal. Thus, internal block  $B_{mn}$  has latency  $L(B_{mn}) = \max(mn/w, d \cdot L(A_n))$ . The latency of the whole system is k/d times this, giving latency  $= \max(mnk/dw, k \cdot L(A_n))$ . Because this datapath utilizes iterative reuse, a new vector cannot enter until the previous vector begins exiting the datapath, so the throughput (in transforms per cycle) is the inverse of the latency,  $\min(dw/mnk, 1/(k \cdot L(A_n)))$ .

- Case 2: No iterative reuse. This case occurs when d=k. Now, no iterative reuse is performed; the data only passes through the inner block once. The datapath consists of d=k stages, giving latency  $=k \cdot L(A_n)$ . Because the data never feeds back, the throughput is limited only by the streaming width, giving throughput =w/mn transforms per cycle.

These equations show that increasing w and d will lead to lower latency and higher throughput in equal weights, until either the data flows so quickly that the latency of the computation dominates  $(d \cdot L(A_n) > mn/w)$ , or d increases until no iterative reuse is performed (d = k).

Flexibility. Additionally, there is one important distinction that must be made between parameters d and w: as w grows, the datapath requires greater bandwidth at its ports, and the cost of interconnect and multiplexers increases. In the simple example considered here, a design with w=2, d=16 will have roughly the same cost and performance as a design with w=16, d=2, but the latter will require a bandwidth of 16 words during loading and unloading phases, while the former only requires two words per cycle (over  $8 \times$  more cycles). For this reason, it is preferable to increase d instead of w. However, d must divide k evenly (k is typically the  $\log_2$  of the transform size). In many cases, this becomes an "all or nothing" situation, where the only options are d=1 and d=k. In those cases, the added flexibility provided by w is important.

Lastly, when the datapath does not employ iterative reuse (i.e., when d=k), the designer typically has a wider choice of algorithms because the internal stages are not required to be uniform.

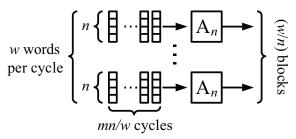

Datapath efficiency and vector interleaving. Assume we have an iterative reuse datapath that reuses block  $B_n$ . Here,  $B_n$  can represent any datapath, including those with further iterative reuse internally.  $B_n$  has an inherent latency  $L(B_n)$  and throughput  $T(B_n)$  (determined by the inverse of the minimum initiation interval of input vectors).

With a single vector recirculating through  $B_n$ , the effective throughput of  $B_n$  may be further limited to  $1/L(B_n)$  if  $L(B_n)$  is greater than the minimum initiation interval. In this case the head of the vector is still inside  $B_n$  when  $B_n$ 's input is ready to accept a new iteration.

Let R be a utilization ratio of the effective throughput to the inherent throughput of  $B_n$ ; this quantifies the portion of  $B_n$ 's potential throughput that is utilized in the system. For a single vector,  $R = (1/L(B_n))/T(B_n)$ .

When the utilization by a single vector is sufficiently low, the system can interleave multiple vectors to make use of the full throughput capacity of  $B_n$ . Formally, if  $R \leq 1/V$  (where V is an integer), the system may interleave V computations through the datapath, increasing the effective throughput and thus increasing the utilization ratio to  $R' = (V/L(B_n))/T(B_n)$ .

In some cases, a designer may want to increase  $L(B_n)$  artificially for better efficiency. For example, if R=0.55, the designer could insert delay buffers in the datapath (increase  $L(B_n)$ ) until R is reduced to 0.5 and then interleave two vectors. This increased utilization yields higher throughput at the expense of added latency, so the designer's particular application requirements will determine the suitability of this approach.

3.5. Summary 34

## 3.5 Summary

This chapter presented a formula-driven hardware paradigm that connects a set of sequential hardware structures with a set of formula constructs. These sequential reuse techniques allow multiple computations from an algorithm to be mapped to a single processing element in the datapath.

First, streaming reuse controls the width of the data vector and thus the parallelism of the system. Using these techniques, streaming implementations require that the computation be decomposed into parallel sub-blocks. The formula  $I_m \otimes A_n$  mathematically captures this requirement for streaming width w, where w is an integer multiple of n and w < mn. This idea is extended when A is allowed to vary with an index variable:  $I_m \otimes_\ell A_\ell^n$ . Now, since different A matrices are allowed, any  $mn \times mn$  matrix that can be decomposed into parallel  $n \times n$  subblocks can be streamed with width w. The more similarity that exists among the different the  $A_\ell^n$  blocks, the lower the implementation cost, because in that case the final hardware block can share computational elements between the different iterations.

Similarly, *iterative reuse* (IR) controls the depth of the datapath, which is the number of cascaded stages from input to output. Designs with higher depth have more stages, while lower depths correspond to fewer stages and thus more iterations of the data vector over the structure. This repeated stage structure is written as  $\prod_{\ell} A_{\ell}^n$ . Note that the  $n \times n$  matrix A can depend on index  $\ell$ . Thus, any product of matrices can be iteratively reused, but if the  $A_{\ell}^n$  matrices are not related, there is no benefit from using IR. For example, if  $A_0^n$  and  $A_1^n$  are completely different and cannot share logic, then there would be no benefit to using IR on  $\prod_{\ell=0}^1 A_{\ell}^n$ , because the IR version would have slightly greater area (due to the feedback path), the same or worse latency, and roughly half of the throughput. In this way, the structure of a formula is deeply connected with whether or not iterative reuse provides a benefit.

Thus, the type and amount of sequential reuse that is desired affects the amount of regularity that is beneficial within an algorithm. For example, the Pease FFT algorithm (2.13) and the Iterative FFT algorithm (2.15) are similar except the Pease algorithm has the same permutation in each of its stages, while the Iterative algorithm does not. So, when the user requests a design with IR, the Pease algorithm is more efficient than the Iterative algorithm. In this way, Spiral does not search to select algorithms, but chooses based upon how well an algorithm's structure fits within the paradigm the

user has requested.

# **Chapter 4**

# **Automatic Compilation from Formula to Datapath**

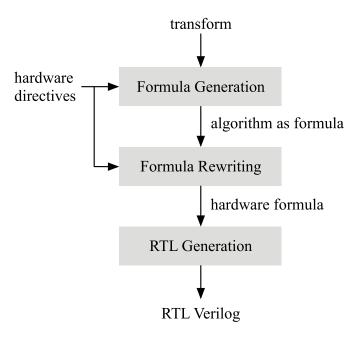

Previous chapters presented a mathematical language for describing linear transform algorithms and how that formula space can be refined to allow explicit specification of sequential reuse. This chapter describes how these concepts are used to drive an automatic compilation framework that maps a transform to an algorithmic formula, transforms the formula to one that includes the desired streaming and iterative reuse characteristics, and maps that hardware formula into a register-transfer level (RTL) Verilog description.

Figure 4.1 shows a high-level view of each of the steps in this compilation process. First, a transform enters the system, an algorithm is selected, and a formula representation of that algorithm is produced. Then, formula rewriting is used to apply iterative reuse and streaming reuse to the formula; the resulting "hardware formula" now has explicit sequential reuse. Lastly, the hardware formula is then translated into a register-transfer level (RTL) Verilog description. Below, each of these steps is explained.

#### 4.1 Hardware Directives

This system uses *hardware directives* to include information about the desired features of the hardware implementation to be produced by the compilation framework. Hardware directives are tags placed around a formula or portion of a formula. This work utilizes two directives. First, the

Figure 4.1: Block diagram of hardware compilation system.

streaming tag indicates streaming reuse:

$$\underbrace{A_n}_{\text{stream}(w)}$$

.

This indicates that the contents of A should be restructured such that the resulting hardware formula will be implemented in a block that contains w input and output ports, with data streamed at w elements per cycle, over n/w cycles.

Next, the *depth tag* indicates whether to employ iterative reuse (and of what depth):

$$\underbrace{A_n}_{\text{depth}(d_0,d_1,\dots)}.$$